bunchcycle.bunchcycle_arc Architecture Reference

Collects pulse information and groups it per bunch crossing. More...

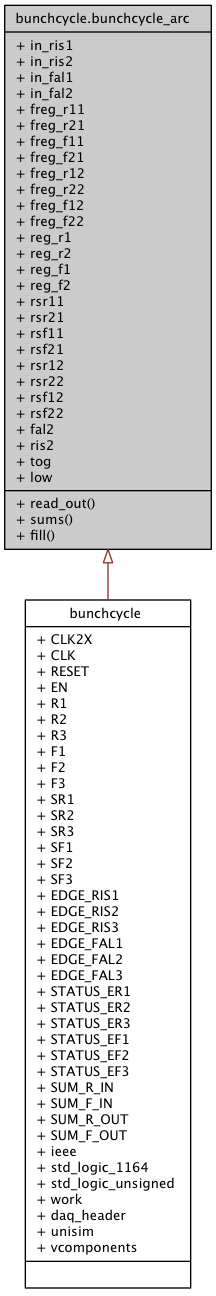

Inheritance diagram for bunchcycle.bunchcycle_arc:

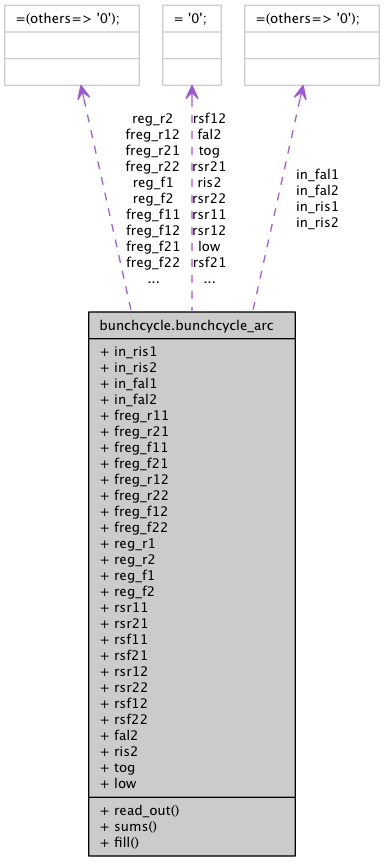

Collaboration diagram for bunchcycle.bunchcycle_arc:

Processes | |

| read_out | ( CLK , RESET ) |

| read registers out | |

| sums | ( CLK2X , RESET ) |

| multiplicity | |

| fill | ( CLK2X , RESET ) |

| fill registers | |

Signals | |

| in_ris1 | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| in_ris2 | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| in_fal1 | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| in_fal2 | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| freg_r11 | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| freg_r21 | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| freg_f11 | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| freg_f21 | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| freg_r12 | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| freg_r22 | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| freg_f12 | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| freg_f22 | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| reg_r1 | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| reg_r2 | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| reg_f1 | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| reg_f2 | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| rsr11 | std_logic := ' 0 ' |

| rsr21 | std_logic := ' 0 ' |

| rsf11 | std_logic := ' 0 ' |

| rsf21 | std_logic := ' 0 ' |

| rsr12 | std_logic := ' 0 ' |

| rsr22 | std_logic := ' 0 ' |

| rsf12 | std_logic := ' 0 ' |

| rsf22 | std_logic := ' 0 ' |

| fal2 | std_logic := ' 0 ' |

| ris2 | std_logic := ' 0 ' |

| tog | std_logic := ' 0 ' |

| low | std_logic := ' 0 ' |

Detailed Description

Collects pulse information and groups it per bunch crossing.Consists of separate input registers for each half of BC, according to status bits values are forwarded to outputs.

Definition at line 77 of file bunchcycle.vhd.

Member Function Documentation

| fill | ( CLK2X , | |

| RESET ) |

fill registers

Definition at line 195 of file bunchcycle.vhd.

00195 fill : process (CLK2X, RESET) 00196 begin -- process fill 00197 if RESET = '1' then -- asynchronous reset (active high) 00198 freg_r11(4 downto 0) <= (others => '0'); 00199 freg_r21(4 downto 0) <= (others => '0'); 00200 freg_f11(4 downto 0) <= (others => '0'); 00201 freg_f21(4 downto 0) <= (others => '0'); 00202 freg_r12(4 downto 0) <= (others => '0'); 00203 freg_r22(4 downto 0) <= (others => '0'); 00204 freg_f12(4 downto 0) <= (others => '0'); 00205 freg_f22(4 downto 0) <= (others => '0'); 00206 rsr12 <= '0'; 00207 rsr22 <= '0'; 00208 rsf12 <= '0'; 00209 rsf22 <= '0'; 00210 rsr11 <= '0'; 00211 rsr21 <= '0'; 00212 rsf11 <= '0'; 00213 rsf21 <= '0'; 00214 tog <= '0'; 00215 elsif CLK2X'event and CLK2X = '1' then -- rising clock edge 00216 if EN = '1' then 00217 00218 tog <= not tog; 00219 -- first half 00220 if tog = '1' then 00221 00222 if (in_fal1 = 0) and (SR1 = '1') then 00223 freg_f11(4 downto 0) <= (others => '1'); 00224 rsf11 <= SF1; 00225 freg_f12(4 downto 0) <= in_fal1; 00226 rsf12 <= SF1; 00227 freg_r11(4 downto 0) <= in_ris1; 00228 rsr11 <= SR1; 00229 freg_r12(4 downto 0) <= in_ris2; 00230 rsr12 <= SR2; 00231 elsif (in_fal2 = 0) and (SR2 = '1') then 00232 freg_f11(4 downto 0) <= in_fal1; 00233 rsf11 <= SF1; 00234 freg_f12(4 downto 0) <= (others => '1'); 00235 rsf12 <= SF2; 00236 freg_r11(4 downto 0) <= in_ris1; 00237 rsr11 <= SR1; 00238 freg_r12(4 downto 0) <= in_ris2; 00239 rsr12 <= SR2; 00240 else 00241 freg_f11(4 downto 0) <= in_fal1; 00242 rsf11 <= SF1; 00243 freg_f12(4 downto 0) <= in_fal2; 00244 rsf12 <= SF2; 00245 freg_r11(4 downto 0) <= in_ris1; 00246 rsr11 <= SR1; 00247 freg_r12(4 downto 0) <= in_ris2; 00248 rsr12 <= SR2; 00249 end if; 00250 00251 -- second half 00252 else 00253 00254 if (in_fal1 = 0) and (SR1 = '1') then 00255 freg_f21(4 downto 0) <= (others => '1'); 00256 rsf21 <= SF1; 00257 freg_f22(4 downto 0) <= in_fal1; 00258 rsf22 <= SF1; 00259 freg_r21(4 downto 0) <= in_ris1; 00260 rsr21 <= SR1; 00261 freg_r22(4 downto 0) <= in_ris2; 00262 rsr22 <= SR2; 00263 elsif (in_fal2 = 0) and (SR2 = '1') then 00264 freg_f21(4 downto 0) <= in_fal1; 00265 rsf21 <= SF1; 00266 freg_f22(4 downto 0) <= (others => '1'); 00267 rsf22 <= SF2; 00268 freg_r21(4 downto 0) <= in_ris1; 00269 rsr21 <= SR1; 00270 freg_r22(4 downto 0) <= in_ris2; 00271 rsr22 <= SR2; 00272 else 00273 freg_f21(4 downto 0) <= in_fal1; 00274 rsf21 <= SF1; 00275 freg_f22(4 downto 0) <= in_fal2; 00276 rsf22 <= SF2; 00277 freg_r21(4 downto 0) <= in_ris1; 00278 rsr21 <= SR1; 00279 freg_r22(4 downto 0) <= in_ris2; 00280 rsr22 <= SR2; 00281 end if; 00282 00283 end if; 00284 00285 else 00286 tog <= '0'; 00287 end if; 00288 end if; 00289 end process fill;

| read_out | ( CLK , | |

| RESET ) |

read registers out

Definition at line 131 of file bunchcycle.vhd.

00131 read_out : process (CLK, RESET) 00132 begin -- process read 00133 if RESET = '1' then -- asynchronous reset (active high) 00134 STATUS_EF1 <= '0'; 00135 STATUS_ER1 <= '0'; 00136 STATUS_EF2 <= '0'; 00137 STATUS_ER2 <= '0'; 00138 EDGE_RIS1 <= (others => '0'); 00139 EDGE_FAL1 <= (others => '0'); 00140 EDGE_RIS2 <= (others => '0'); 00141 EDGE_FAL2 <= (others => '0'); 00142 elsif CLK'event and CLK = '1' then -- rising clock edge 00143 if (reg_f1 > reg_f2) and (fal2 = '1') then 00144 EDGE_FAL2 <= reg_f1; 00145 EDGE_FAL1 <= reg_f2; 00146 else 00147 EDGE_FAL2 <= reg_f2; 00148 EDGE_FAL1 <= reg_f1; 00149 end if; 00150 if (reg_r1 > reg_r2) and (ris2 = '1') then 00151 EDGE_RIS1 <= reg_r2; 00152 EDGE_RIS2 <= reg_r1; 00153 else 00154 EDGE_RIS1 <= reg_r1; 00155 EDGE_RIS2 <= reg_r2; 00156 end if; 00157 STATUS_EF1 <= rsf11 or rsf21; 00158 STATUS_ER1 <= rsr11 or rsr21; 00159 STATUS_EF2 <= fal2; 00160 STATUS_ER2 <= ris2; 00161 end if; 00162 end process read_out;

| sums | ( CLK2X , | |

| RESET ) |

multiplicity

Definition at line 168 of file bunchcycle.vhd.

00168 sums : process (CLK2X, RESET) 00169 begin -- process sums 00170 if RESET = '1' then -- asynchronous reset (active high) 00171 SUM_R_OUT <= (others => '0'); 00172 SUM_F_OUT <= (others => '0'); 00173 elsif CLK2X'event and CLK2X = '1' then -- rising clock edge 00174 SUM_R_OUT <= ("0000000" & SR1) + ("0000000" & SR2); 00175 SUM_F_OUT <= ("0000000" & SF1) + ("0000000" & SF2); 00176 end if; 00177 end process sums;

The documentation for this class was generated from the following file: