bcm_rod_treadmil.bcm_rod_treadmil_arc Architecture Reference

ROD treadmill. More...

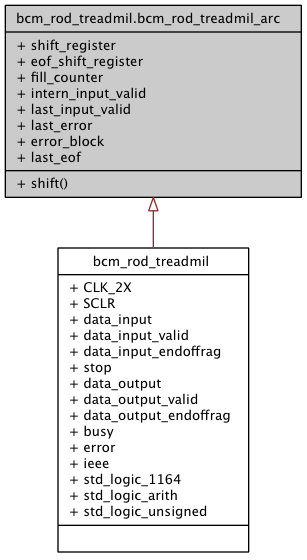

Inheritance diagram for bcm_rod_treadmil.bcm_rod_treadmil_arc:

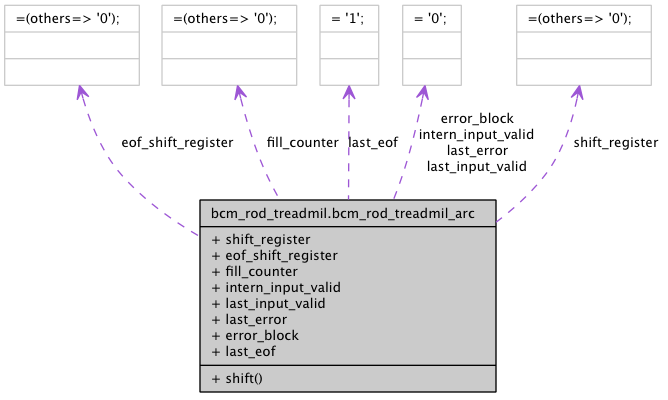

Collaboration diagram for bcm_rod_treadmil.bcm_rod_treadmil_arc:

Processes | |

| shift | ( CLK_2X ) |

| organize data, see comments within code | |

Signals | |

| shift_register | std_logic_vector ( 223 downto 0 ) := ( others = > ' 0 ' ) |

| eof_shift_register | std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

| fill_counter | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| intern_input_valid | std_logic := ' 0 ' |

| last_input_valid | std_logic := ' 0 ' |

| last_error | std_logic := ' 0 ' |

| error_block | std_logic := ' 0 ' |

| last_eof | std_logic := ' 1 ' |

Detailed Description

ROD treadmill.The ROD treadmil is the input port of the ROD. It is a 224-bit wide shift register clock with the doubled clock (80 MHz) "CLK_2X". With a "data_input_valid" (a high 40 Mbit/s pulse) the 224-bit wide "shift_register" is filled. If the shift register is resetted or if it is not empty its "busy" is high. If a "data_input_valid" arrives during the busy an "error" is latched until the end of the data block. The shifting of the register can be stopped by the "stop" signal and the shifting continues when "stop" is low again. Valid output data are accompanied with a "data_output_valid" signal.

Definition at line 82 of file bcm_rod_treadmil.vhd.

Member Function Documentation

| shift | ( CLK_2X ) |

organize data, see comments within code

Definition at line 96 of file bcm_rod_treadmil.vhd.

00096 shift : process (CLK_2X) 00097 begin 00098 if (CLK_2X'event and CLK_2X = '1') then 00099 if (SCLR = '1') then -- synchronous clear (reset) 00100 data_output <= (others => '0'); 00101 data_output_valid <= '0'; 00102 data_output_endoffrag <= '0'; 00103 busy <= '1'; 00104 error <= '0'; 00105 shift_register <= (others => '0'); 00106 eof_shift_register <= (others => '0'); 00107 fill_counter <= (others => '0'); 00108 intern_input_valid <= '0'; 00109 last_input_valid <= '0'; 00110 last_error <= '0'; 00111 error_block <= '0'; 00112 last_eof <= '1'; 00113 else 00114 intern_input_valid <= data_input_valid; 00115 last_input_valid <= intern_input_valid; 00116 if (data_input_valid = '1' and last_input_valid = '0' and fill_counter = "000") then -- shift register empty and data to fill available 00117 if (stop = '0') then -- output not stopped - can put first word directly to output and store rest in shift register 00118 data_output_valid <= '1'; 00119 data_output_endoffrag <= '0'; 00120 if (last_eof = '1') then 00121 data_output <= data_input(31 downto 0); 00122 shift_register <= X"00000000" & data_input(223 downto 32); 00123 eof_shift_register <= "0" & data_input_endoffrag & "00000"; 00124 fill_counter <= "110"; 00125 else -- skip LVL1ID 00126 data_output <= data_input(63 downto 32); 00127 shift_register <= X"00000000_00000000" & data_input(223 downto 64); 00128 eof_shift_register <= "00" & data_input_endoffrag & "0000"; 00129 fill_counter <= "101"; 00130 end if; 00131 else -- output stopped - store entire input in shift register 00132 data_output <= (others => '0'); 00133 data_output_valid <= '0'; 00134 data_output_endoffrag <= '0'; 00135 if (last_eof = '1') then 00136 shift_register <= data_input(223 downto 0); 00137 eof_shift_register <= data_input_endoffrag & "000000"; 00138 fill_counter <= "111"; 00139 else -- skip LVL1ID 00140 shift_register <= X"00000000" & data_input(223 downto 32); 00141 eof_shift_register <= "0" & data_input_endoffrag & "00000"; 00142 fill_counter <= "110"; 00143 end if; 00144 end if; 00145 last_eof <= data_input_endoffrag; 00146 busy <= '1'; 00147 error <= '0'; -- data could be stored in shift register 00148 last_error <= '0'; -- new data block, clear error latch 00149 error_block <= '1'; -- to avoid error in 2nd data_input_valid pulse clock cycle 00150 elsif (not (fill_counter = "000")) then -- shift register not empty 00151 if (stop = '0') then -- output not stopped - shift out data 00152 data_output <= shift_register(31 downto 0); 00153 data_output_valid <= '1'; 00154 data_output_endoffrag <= eof_shift_register(0); 00155 shift_register <= X"00000000" & shift_register(223 downto 32); 00156 eof_shift_register <= "0" & eof_shift_register(6 downto 1); 00157 fill_counter <= fill_counter - "1"; 00158 else -- output stopped - do not shift out data 00159 data_output <= (others => '0'); 00160 data_output_valid <= '0'; 00161 data_output_endoffrag <= '0'; 00162 shift_register <= shift_register; 00163 eof_shift_register <= eof_shift_register; 00164 fill_counter <= fill_counter; 00165 end if; 00166 busy <= '1'; 00167 if (data_input_valid = '1' and error_block = '0') then -- data to fill available but shift register not empty and not 2nd data_input_valid pulse clock cycle 00168 error <= '1'; -- data could not be stored in shift register 00169 last_error <= '1'; -- set error latch 00170 else -- keep error state if error latched 00171 error <= last_error; 00172 last_error <= last_error; 00173 end if; 00174 error_block <= '0'; 00175 else -- shift register empty and no data to fill available 00176 data_output <= (others => '0'); 00177 data_output_valid <= '0'; 00178 data_output_endoffrag <= '0'; 00179 busy <= '0'; 00180 error <= '0'; 00181 shift_register <= (others => '0'); 00182 fill_counter <= (others => '0'); 00183 last_error <= '0'; 00184 error_block <= '0'; 00185 end if; 00186 end if; 00187 end if; 00188 end process shift;

The documentation for this class was generated from the following file: