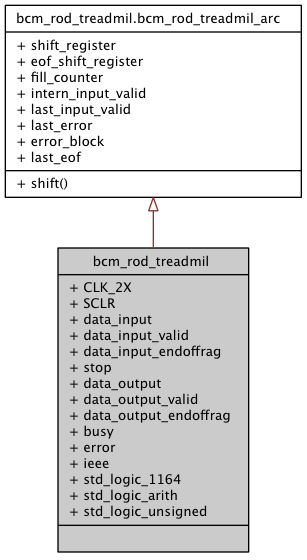

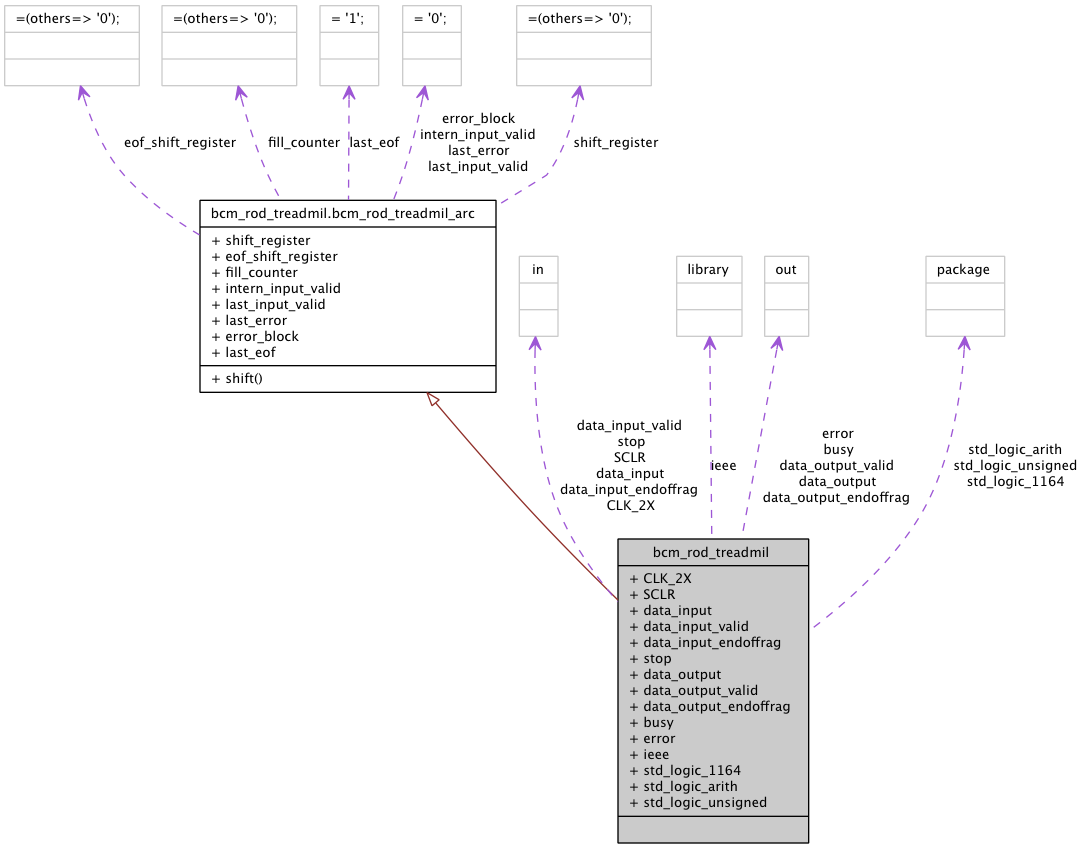

bcm_rod_treadmil Entity Reference

ROD treadmill. More...

Architectures | |

| bcm_rod_treadmil_arc | Architecture |

| ROD treadmill. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

Ports | |

| CLK_2X | in std_logic |

| 80 MHz clock | |

| SCLR | in std_logic |

| synchronous clear (reset) signal | |

| data_input | in std_logic_vector ( 223 downto 0 ) |

| 224-bit wide data input bus | |

| data_input_valid | in std_logic |

| input data valid indicator signal | |

| data_input_endoffrag | in std_logic |

| input data end of fragment indicator signal | |

| stop | in std_logic |

| backpressure indicator signal | |

| data_output | out std_logic_vector ( 31 downto 0 ) |

| 32-bit wide data output bus | |

| data_output_valid | out std_logic |

| output data valid indicator signal | |

| data_output_endoffrag | out std_logic |

| output data end of fragment indicator signal | |

| busy | out std_logic |

| busy indicator signal | |

| error | out std_logic |

| latched data corruption error indicator signal | |

Detailed Description

ROD treadmill.The ROD treadmil is the input port of the ROD. It is a 224-bit wide shift register clock with the doubled clock (80 MHz) "CLK_2X". With a "data_input_valid" (a high 40 Mbit/s pulse) the 224-bit wide "shift_register" is filled. If the shift register is resetted or if it is not empty its "busy" is high. If a "data_input_valid" arrives during the busy an "error" is latched until the end of the data block. The shifting of the register can be stopped by the "stop" signal and the shifting continues when "stop" is low again. Valid output data are accompanied with a "data_output_valid" signal.

Definition at line 58 of file bcm_rod_treadmil.vhd.

Member Data Documentation

busy out std_logic [Port] |

CLK_2X in std_logic [Port] |

data_input in std_logic_vector ( 223 downto 0 ) [Port] |

data_input_endoffrag in std_logic [Port] |

data_input_valid in std_logic [Port] |

data_output out std_logic_vector ( 31 downto 0 ) [Port] |

data_output_endoffrag out std_logic [Port] |

data_output_valid out std_logic [Port] |

error out std_logic [Port] |

ieee library [Library] |

SCLR in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 46 of file bcm_rod_treadmil.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 48 of file bcm_rod_treadmil.vhd.

stop in std_logic [Port] |

The documentation for this class was generated from the following file: