bcm_rod_slink.bcm_rod_slink_arc Architecture Reference

S-Link interface. More...

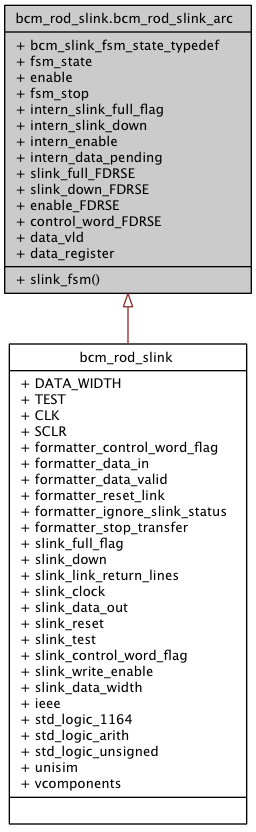

Inheritance diagram for bcm_rod_slink.bcm_rod_slink_arc:

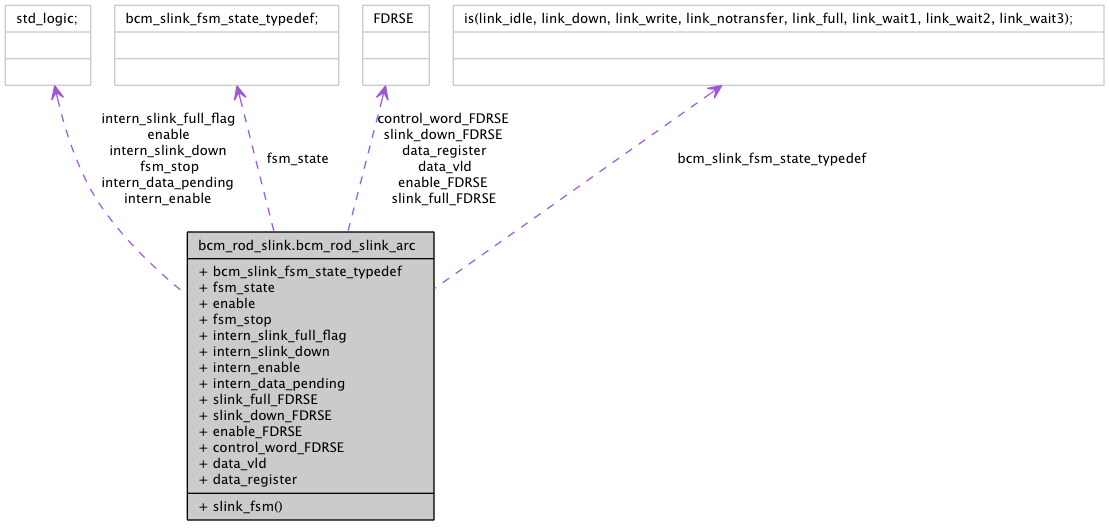

Collaboration diagram for bcm_rod_slink.bcm_rod_slink_arc:

Processes | |

| slink_fsm | ( CLK , SCLR ) |

| S-Link FSM. | |

Types | |

| bcm_slink_fsm_state_typedef | ( link_idle , link_down , link_write , link_notransfer , link_full , link_wait1 , link_wait2 , link_wait3 ) |

| S-Link FSM states. | |

Signals | |

| fsm_state | bcm_slink_fsm_state_typedef |

| enable | std_logic |

| fsm_stop | std_logic |

| intern_slink_full_flag | std_logic |

| intern_slink_down | std_logic |

| intern_enable | std_logic |

| intern_data_pending | std_logic |

Component Instantiations | |

| slink_full_FDRSE | FDRSE |

| FF primitive, synchronous set/reset. | |

| slink_down_FDRSE | FDRSE |

| FF primitive, synchronous set/reset, pos clk edge. | |

| enable_FDRSE | FDRSE |

| FF primitive, synchronous set/reset, pos clk edge. | |

| control_word_FDRSE | FDRSE |

| FF primitive, synchronous set/reset, pos clk edge. | |

| data_vld | FDRSE |

| FF primitive, synchronous set/reset, pos clk edge. | |

| data_register | FDRSE |

| FF primitive, synchronous set/reset, pos clk edge. | |

Detailed Description

S-Link interface.Definition at line 71 of file bcm_rod_slink.vhd.

Member Function Documentation

| slink_fsm | ( CLK , | |

| SCLR ) |

S-Link FSM.

Definition at line 185 of file bcm_rod_slink.vhd.

00185 slink_fsm : process (CLK, SCLR) 00186 begin 00187 if (SCLR = '1') then 00188 fsm_state <= link_idle; 00189 fsm_stop <= '1'; 00190 slink_write_enable <= '1'; 00191 elsif (CLK'event and CLK = '1') then 00192 if (intern_slink_down = '0' and formatter_ignore_slink_status = '0') then 00193 fsm_state <= link_down; 00194 fsm_stop <= '1'; 00195 slink_write_enable <= '1'; 00196 else 00197 case fsm_state is 00198 when link_idle => 00199 fsm_stop <= '0'; 00200 if (formatter_data_valid = '1') then 00201 fsm_state <= link_write; 00202 slink_write_enable <= '0'; 00203 else 00204 fsm_state <= link_notransfer; 00205 end if; 00206 when link_write => 00207 if ((intern_slink_full_flag = '1' or formatter_ignore_slink_status = '1') and formatter_data_valid = '0') then 00208 fsm_state <= link_notransfer; 00209 slink_write_enable <= '1'; 00210 elsif (intern_slink_full_flag = '0' and formatter_ignore_slink_status = '0') then 00211 fsm_state <= link_full; 00212 slink_write_enable <= '1'; 00213 else 00214 fsm_state <= link_write; 00215 end if; 00216 when link_notransfer => 00217 if ((intern_slink_full_flag = '1' or formatter_ignore_slink_status = '1') and formatter_data_valid = '1') then 00218 fsm_state <= link_write; 00219 slink_write_enable <= '0'; 00220 elsif (intern_slink_full_flag = '0' and formatter_ignore_slink_status = '0') then 00221 fsm_state <= link_full; 00222 else 00223 fsm_state <= link_notransfer; 00224 end if; 00225 when link_full => 00226 if (formatter_ignore_slink_status = '1') then 00227 -- After a reset the ignore SlinkStatus might be set to '0'. 00228 -- if there is active ('0') lff line the STM ends up in the 00229 -- LinkFull_state. In order to ignore the lff there must be 00230 -- a way to escape the state if the ignoreSlinkStatus line 00231 -- is set to '1' later. Therfore this condition here. 00232 fsm_state <= link_idle; 00233 elsif (intern_slink_full_flag = '1' and intern_data_pending = '1') then 00234 fsm_state <= link_write; 00235 slink_write_enable <= '0'; 00236 elsif (intern_slink_full_flag = '1' and intern_data_pending = '0') then 00237 fsm_state <= link_notransfer; 00238 else 00239 fsm_state <= link_full; 00240 end if; 00241 when link_down => 00242 fsm_state <= link_wait1; 00243 when link_wait1 => 00244 fsm_state <= link_wait2; 00245 when link_wait2 => 00246 fsm_state <= link_wait3; 00247 when link_wait3 => 00248 fsm_state <= link_idle; 00249 fsm_stop <= '0'; 00250 end case; 00251 end if; 00252 end if; 00253 end process slink_fsm;

Member Data Documentation

bcm_slink_fsm_state_typedef ( link_idle , link_down , link_write , link_notransfer , link_full , link_wait1 , link_wait2 , link_wait3 ) [Type] |

control_word_FDRSE FDRSE [Component Instantiation] |

FF primitive, synchronous set/reset, pos clk edge.

Definition at line 142 of file bcm_rod_slink.vhd.

data_register FDRSE [Component Instantiation] |

FF primitive, synchronous set/reset, pos clk edge.

Definition at line 170 of file bcm_rod_slink.vhd.

data_vld FDRSE [Component Instantiation] |

FF primitive, synchronous set/reset, pos clk edge.

Definition at line 155 of file bcm_rod_slink.vhd.

enable_FDRSE FDRSE [Component Instantiation] |

FF primitive, synchronous set/reset, pos clk edge.

Definition at line 129 of file bcm_rod_slink.vhd.

slink_down_FDRSE FDRSE [Component Instantiation] |

FF primitive, synchronous set/reset, pos clk edge.

Definition at line 116 of file bcm_rod_slink.vhd.

slink_full_FDRSE FDRSE [Component Instantiation] |

The documentation for this class was generated from the following file: