bcm_rod_slink Entity Reference

S-Link interface. More...

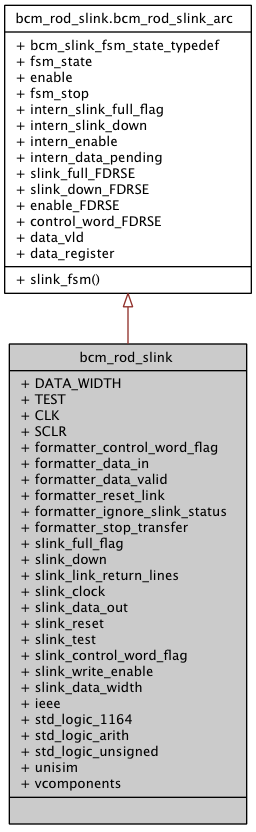

Inheritance diagram for bcm_rod_slink:

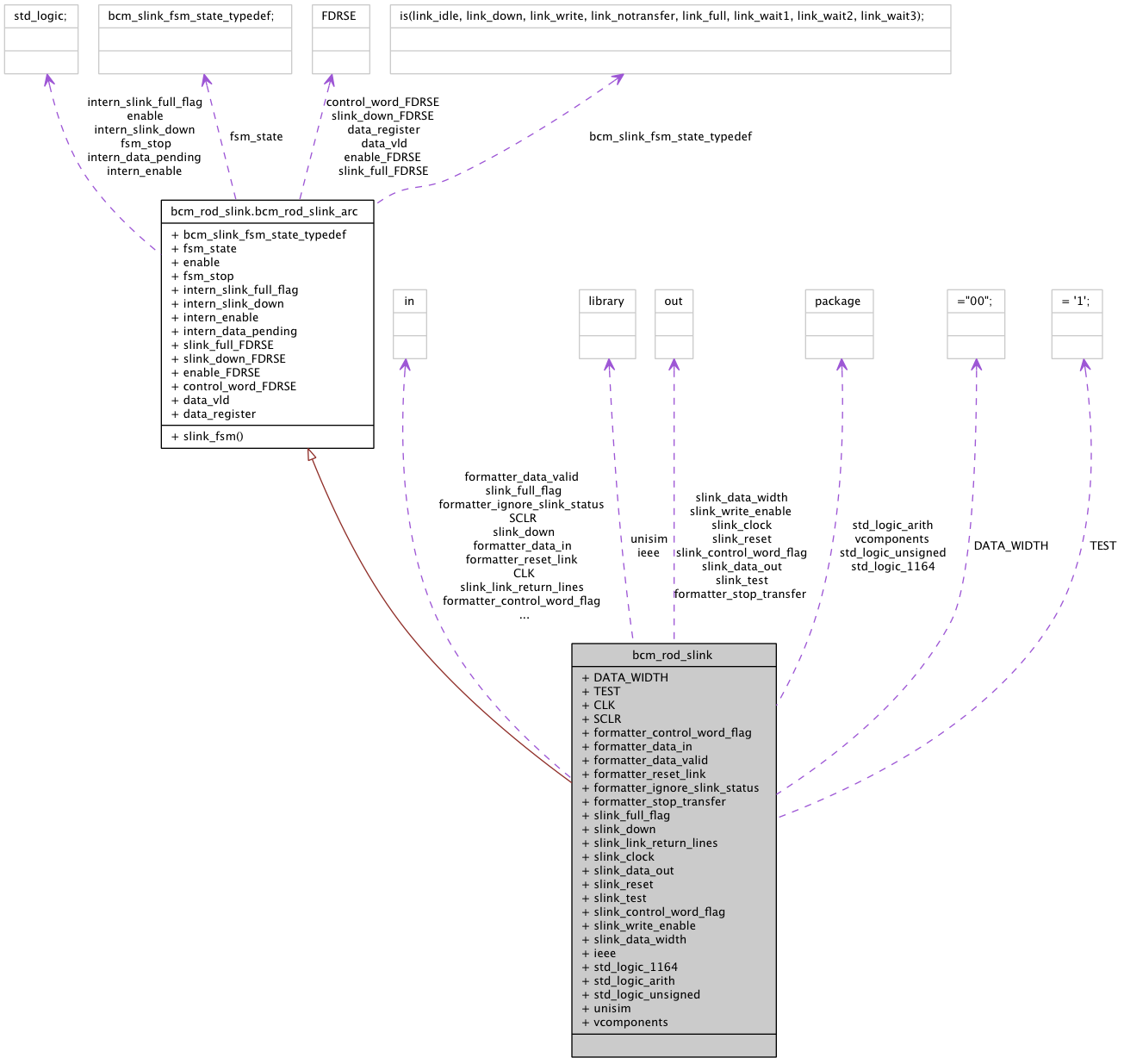

Collaboration diagram for bcm_rod_slink:

Architectures | |

| bcm_rod_slink_arc | Architecture |

| S-Link interface. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

| Library with Xilinx primitives. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| vcomponents | |

| Header with Xilinx primitives. | |

Generics | |

| DATA_WIDTH | std_logic_vector ( 1 downto 0 ) := " 00 " |

| data width | |

| TEST | std_logic := ' 1 ' |

| ACTIVE LOW !!! -> disabled. | |

Ports | |

| CLK | in std_logic |

| 40 MHz clock | |

| SCLR | in std_logic |

| synchronous clear (reset) signal | |

| formatter_control_word_flag | in std_logic |

| signal a control word | |

| formatter_data_in | in std_logic_vector ( 31 downto 0 ) |

| formatter data input | |

| formatter_data_valid | in std_logic |

| formatter indicates valid data | |

| formatter_reset_link | in std_logic |

| formatter reset link | |

| formatter_ignore_slink_status | in std_logic |

| formatter if '1' does not activate formatter_stop_transfer | |

| formatter_stop_transfer | out std_logic |

| formatter full flag | |

| slink_full_flag | in std_logic |

| SLINK full flag (LFF) !!! ACTIVE LOW !!! | |

| slink_down | in std_logic |

| SLINK down (LDOWN) !!! ACTIVE LOW !!! | |

| slink_link_return_lines | in std_logic_vector ( 3 downto 0 ) |

| SLINK return data lines (LRL) !!! NOT USED !!! | |

| slink_clock | out std_logic |

| SLINK clock (UCLK). | |

| slink_data_out | out std_logic_vector ( 31 downto 0 ) |

| SLINK data output (UD). | |

| slink_reset | out std_logic |

| SLINK reset link (URESET) !!! ACTIVE LOW !!! | |

| slink_test | out std_logic |

| SLINK test line (UTEST) !!! ACTIVE LOW !!! | |

| slink_control_word_flag | out std_logic |

| SLINK control word flag (UCTRL) !!! ACTIVE LOW !!! | |

| slink_write_enable | out std_logic |

| SLINK write enable (UWEN) !!! ACTIVE LOW !!! | |

| slink_data_width | out std_logic_vector ( 1 downto 0 ) := " 00 " |

| SLINK data width (UDW) "00"=32-bit, "01"=16-bit, "10"=8-bit, "11"=reserved. | |

Detailed Description

S-Link interface.ROD for the BCM module based on the AtlasRODFormatter by Christoph Schwick.

Definition at line 41 of file bcm_rod_slink.vhd.

Member Data Documentation

CLK in std_logic [Port] |

DATA_WIDTH std_logic_vector ( 1 downto 0 ) := " 00 " [Generic] |

formatter_control_word_flag in std_logic [Port] |

formatter_data_in in std_logic_vector ( 31 downto 0 ) [Port] |

formatter_data_valid in std_logic [Port] |

formatter_ignore_slink_status in std_logic [Port] |

formatter if '1' does not activate formatter_stop_transfer

Definition at line 54 of file bcm_rod_slink.vhd.

formatter_reset_link in std_logic [Port] |

formatter_stop_transfer out std_logic [Port] |

ieee library [Library] |

SCLR in std_logic [Port] |

slink_clock out std_logic [Port] |

slink_control_word_flag out std_logic [Port] |

slink_data_out out std_logic_vector ( 31 downto 0 ) [Port] |

slink_data_width out std_logic_vector ( 1 downto 0 ) := " 00 " [Port] |

SLINK data width (UDW) "00"=32-bit, "01"=16-bit, "10"=8-bit, "11"=reserved.

Definition at line 66 of file bcm_rod_slink.vhd.

slink_down in std_logic [Port] |

slink_full_flag in std_logic [Port] |

slink_link_return_lines in std_logic_vector ( 3 downto 0 ) [Port] |

slink_reset out std_logic [Port] |

slink_test out std_logic [Port] |

slink_write_enable out std_logic [Port] |

std_logic_1164 package [Package] |

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 28 of file bcm_rod_slink.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file bcm_rod_slink.vhd.

TEST std_logic := ' 1 ' [Generic] |

unisim library [Library] |

vcomponents package [Package] |

The documentation for this class was generated from the following file: