bcm_rod_ram.bcm_rod_ram_arc Architecture Reference

DPRAM wrapper with RAM support logic. More...

Inheritance diagram for bcm_rod_ram.bcm_rod_ram_arc:

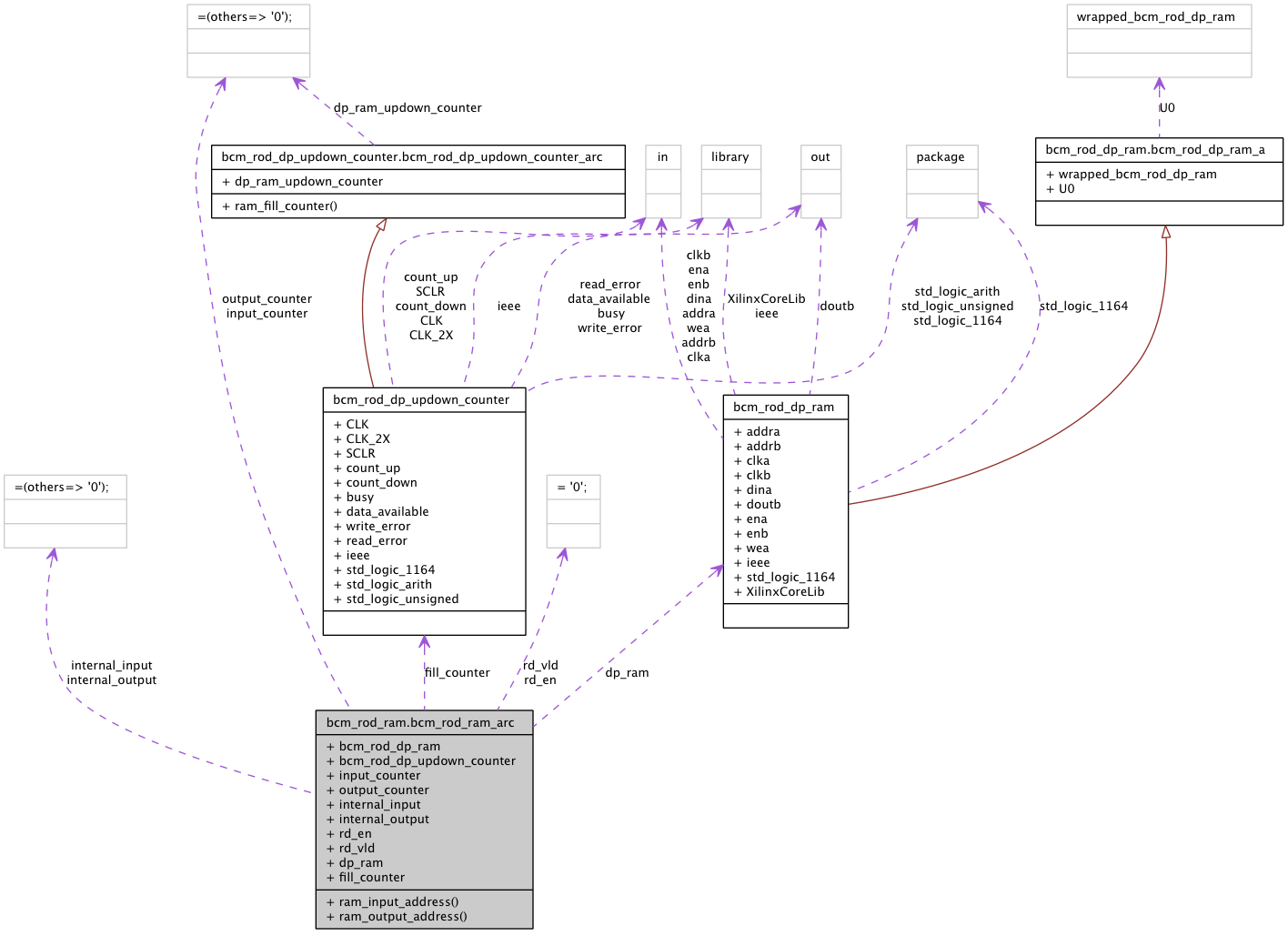

Collaboration diagram for bcm_rod_ram.bcm_rod_ram_arc:

Processes | |

| ram_input_address | ( CLK_2X , SCLR ) |

| generate write address | |

| ram_output_address | ( CLK , SCLR ) |

| generate read address | |

Components | |

| bcm_rod_dp_ram | <Entity bcm_rod_dp_ram> |

| DPRAM. | |

| bcm_rod_dp_updown_counter | <Entity bcm_rod_dp_updown_counter> |

| Up-Down counter. | |

Signals | |

| input_counter | std_logic_vector ( 8 downto 0 ) := ( others = > ' 0 ' ) |

| output_counter | std_logic_vector ( 8 downto 0 ) := ( others = > ' 0 ' ) |

| internal_input | std_logic_vector ( 32 downto 0 ) := ( others = > ' 0 ' ) |

| internal_output | std_logic_vector ( 32 downto 0 ) := ( others = > ' 0 ' ) |

| rd_en | std_logic := ' 0 ' |

| rd_vld | std_logic := ' 0 ' |

Component Instantiations | |

| dp_ram | bcm_rod_dp_ram <Entity bcm_rod_dp_ram> |

| DPRAM. | |

| fill_counter | bcm_rod_dp_updown_counter <Entity bcm_rod_dp_updown_counter> |

| Up-Down counter. | |

Detailed Description

DPRAM wrapper with RAM support logic.Definition at line 55 of file bcm_rod_ram.vhd.

Member Function Documentation

| ram_input_address | ( CLK_2X , | |

| SCLR ) |

generate write address

Definition at line 134 of file bcm_rod_ram.vhd.

00134 ram_input_address : process(CLK_2X, SCLR) 00135 begin 00136 if SCLR = '1' then 00137 input_counter <= (others => '0'); 00138 else 00139 if CLK_2X'event and CLK_2X = '1' then 00140 if data_input_valid = '1' then 00141 input_counter <= (input_counter + "01"); 00142 end if; 00143 end if; 00144 end if; 00145 end process ram_input_address;

| ram_output_address | ( CLK , | |

| SCLR ) |

generate read address

Definition at line 148 of file bcm_rod_ram.vhd.

00148 ram_output_address : process(CLK, SCLR) 00149 begin 00150 if SCLR = '1' then 00151 output_counter <= (others => '0'); 00152 else 00153 if CLK'event and CLK = '1' then 00154 if data_output_next = '1' then 00155 output_counter <= (output_counter + "01"); 00156 end if; 00157 end if; 00158 end if; 00159 end process ram_output_address;

Member Data Documentation

bcm_rod_dp_ram [Component] |

bcm_rod_dp_updown_counter [Component] |

dp_ram bcm_rod_dp_ram [Component Instantiation] |

fill_counter bcm_rod_dp_updown_counter [Component Instantiation] |

The documentation for this class was generated from the following file: