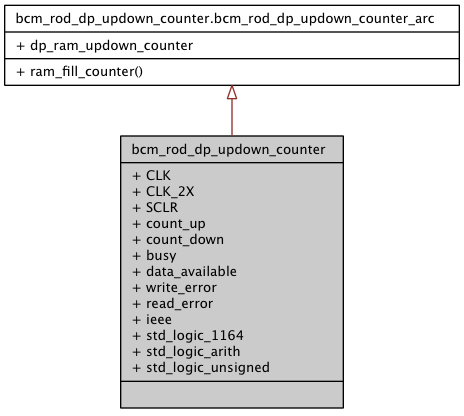

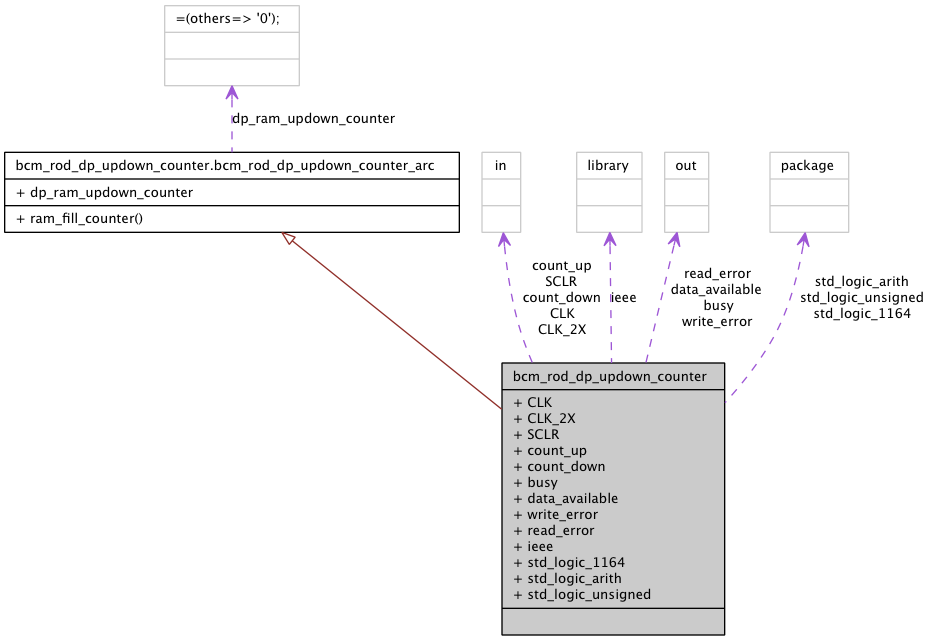

bcm_rod_dp_updown_counter Entity Reference

Up-Down Counter. More...

Architectures | |

| bcm_rod_dp_updown_counter_arc | Architecture |

| up-down counter More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

Ports | |

| CLK | in std_logic |

| 40 MHz clock | |

| CLK_2X | in std_logic |

| 80 MHz clock | |

| SCLR | in std_logic |

| synchronous clear (reset) signal | |

| count_up | in std_logic |

| 80 MHz clocked count up flag | |

| count_down | in std_logic |

| 40 MHz clocked count down flag | |

| busy | out std_logic |

| busy indicator signal | |

| data_available | out std_logic |

| output data valid indicator signal | |

| write_error | out std_logic |

| write data corruption error indicator signal | |

| read_error | out std_logic |

| read data corruption error indicator signal | |

Detailed Description

Up-Down Counter.Dual speed (80 MHz count up and 40 MHz count down) up/down counter. "busy" is high if "dp_ram_updown_counter" is at highest count "data_available" is high if "dp_ram_updown_counter" is not a lowest count "write_error" is high if "count_up" during "dp_ram_updown_counter" is at highest count "read_error" is high if "count_down" during "dp_ram_updown_counter" is at lowest count

Definition at line 38 of file bcm_rod_dp_updown_counter.vhd.

Member Data Documentation

busy out std_logic [Port] |

CLK in std_logic [Port] |

CLK_2X in std_logic [Port] |

count_down in std_logic [Port] |

count_up in std_logic [Port] |

data_available out std_logic [Port] |

ieee library [Library] |

read_error out std_logic [Port] |

read data corruption error indicator signal

Definition at line 50 of file bcm_rod_dp_updown_counter.vhd.

SCLR in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 28 of file bcm_rod_dp_updown_counter.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file bcm_rod_dp_updown_counter.vhd.

write_error out std_logic [Port] |

write data corruption error indicator signal

Definition at line 49 of file bcm_rod_dp_updown_counter.vhd.

The documentation for this class was generated from the following file: