BID_cnt Entity Reference

Bunch-Counter. More...

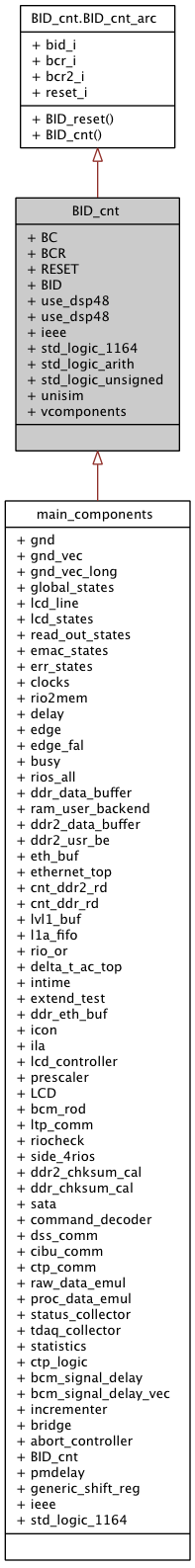

Inheritance diagram for BID_cnt:

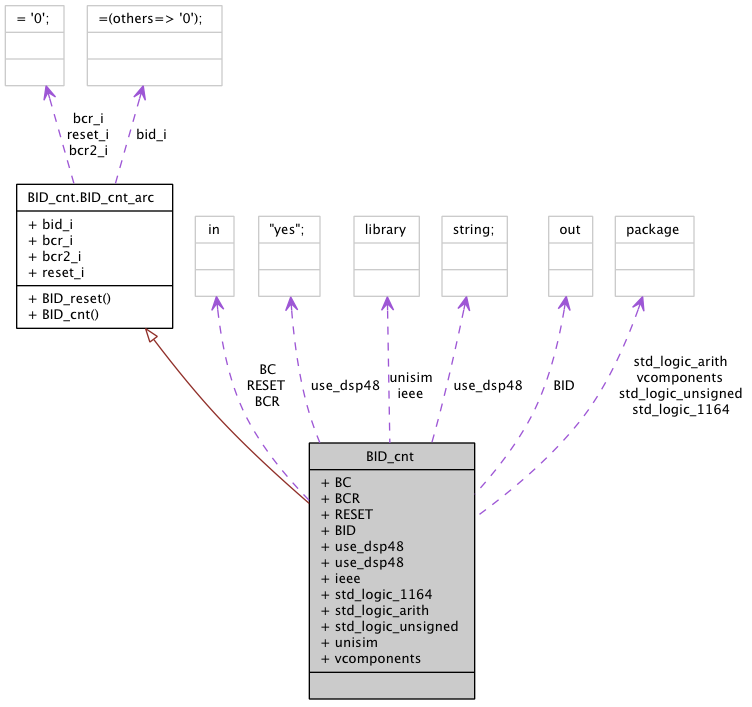

Collaboration diagram for BID_cnt:

Architectures | |

| BID_cnt_arc | Architecture |

| Bunch-Counter. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

| Library with Xilinx primitives. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| vcomponents | |

| Header with Xilinx primitives. | |

Ports | |

| BC | in std_logic |

| Bunch clock. | |

| BCR | in std_logic |

| Bunch counter reset. | |

| RESET | in std_logic |

| Reset. | |

| BID | out std_logic_vector ( 11 downto 0 ) |

| Current bunch ID. | |

Attributes | |

| use_dsp48 | string |

| XST specific attribute for DSP cores. | |

| use_dsp48 | " yes " |

| force XST to infer DSP48 cores | |

Detailed Description

Bunch-Counter.This Entity counts LHC bunch crossings by taking the bunch clock from the LTP as a reference. Get reset by the BCR, also from the LTP

Definition at line 40 of file BID_cnt.vhd.

Member Data Documentation

BC in std_logic [Port] |

BCR in std_logic [Port] |

BID out std_logic_vector ( 11 downto 0 ) [Port] |

ieee library [Library] |

RESET in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 26 of file BID_cnt.vhd.

std_logic_arith package [Package] |

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file BID_cnt.vhd.

unisim library [Library] |

use_dsp48 " yes " [Attribute] |

use_dsp48 string [Attribute] |

vcomponents package [Package] |

The documentation for this class was generated from the following file: