intime Entity Reference

narrow in-time time window More...

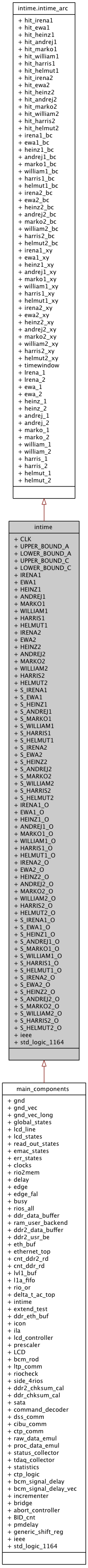

Inheritance diagram for intime:

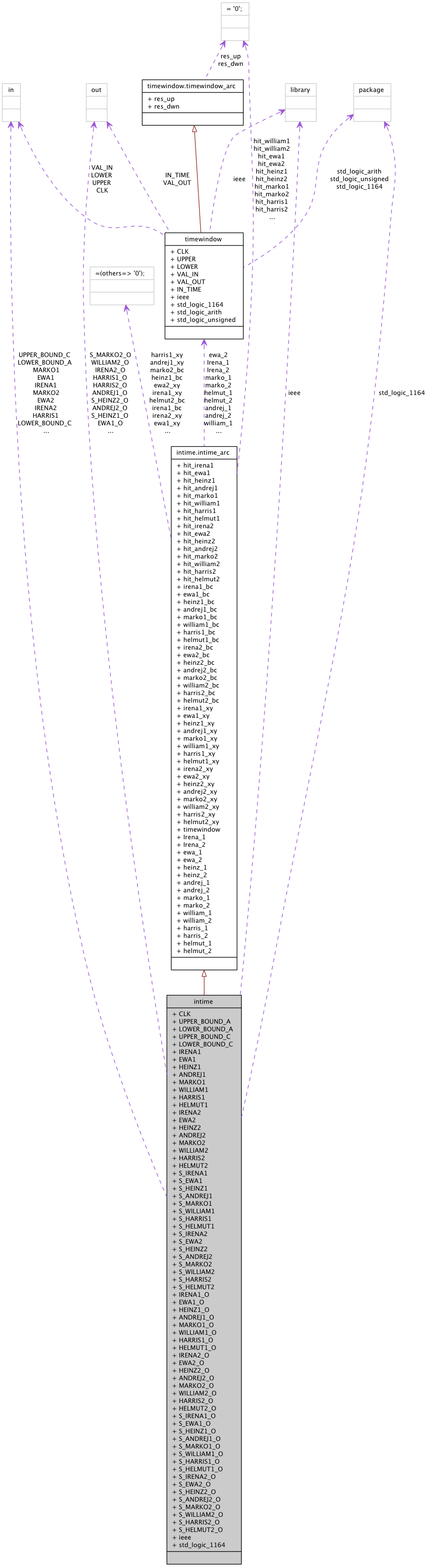

Collaboration diagram for intime:

Architectures | |

| intime_arc | Architecture |

| narrow in-time time window More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

Ports | |

| CLK | in std_logic |

| Clock. | |

| UPPER_BOUND_A | in std_logic_vector ( 5 downto 0 ) := " 101110 " |

| Time window upper boundary side A. | |

| LOWER_BOUND_A | in std_logic_vector ( 5 downto 0 ) := " 010000 " |

| Time window lower boundary side A. | |

| UPPER_BOUND_C | in std_logic_vector ( 5 downto 0 ) := " 101110 " |

| Time window upper boundary side C. | |

| LOWER_BOUND_C | in std_logic_vector ( 5 downto 0 ) := " 010000 " |

| Time window lower boundary side C. | |

| IRENA1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| EWA1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| HEINZ1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| ANDREJ1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| MARKO1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| WILLIAM1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| HARRIS1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| HELMUT1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| IRENA2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| EWA2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| HEINZ2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| ANDREJ2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| MARKO2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| WILLIAM2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| HARRIS2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| HELMUT2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data in | |

| S_IRENA1 | in std_logic |

| 1 CH status bit in | |

| S_EWA1 | in std_logic |

| 1 CH status bit in | |

| S_HEINZ1 | in std_logic |

| 1 CH status bit in | |

| S_ANDREJ1 | in std_logic |

| 1 CH status bit in | |

| S_MARKO1 | in std_logic |

| 1 CH status bit in | |

| S_WILLIAM1 | in std_logic |

| 1 CH status bit in | |

| S_HARRIS1 | in std_logic |

| 1 CH status bit in | |

| S_HELMUT1 | in std_logic |

| 1 CH status bit in | |

| S_IRENA2 | in std_logic |

| 1 CH status bit in | |

| S_EWA2 | in std_logic |

| 1 CH status bit in | |

| S_HEINZ2 | in std_logic |

| 1 CH status bit in | |

| S_ANDREJ2 | in std_logic |

| 1 CH status bit in | |

| S_MARKO2 | in std_logic |

| 1 CH status bit in | |

| S_WILLIAM2 | in std_logic |

| 1 CH status bit in | |

| S_HARRIS2 | in std_logic |

| 1 CH status bit in | |

| S_HELMUT2 | in std_logic |

| 1 CH status bit in | |

| IRENA1_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| EWA1_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| HEINZ1_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| ANDREJ1_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| MARKO1_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| WILLIAM1_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| HARRIS1_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| HELMUT1_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| IRENA2_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| EWA2_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| HEINZ2_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| ANDREJ2_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| MARKO2_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| WILLIAM2_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| HARRIS2_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| HELMUT2_O | out std_logic_vector ( 7 downto 0 ) |

| 1 CH data out | |

| S_IRENA1_O | out std_logic |

| 1 CH status bit out | |

| S_EWA1_O | out std_logic |

| 1 CH status bit out | |

| S_HEINZ1_O | out std_logic |

| 1 CH status bit out | |

| S_ANDREJ1_O | out std_logic |

| 1 CH status bit out | |

| S_MARKO1_O | out std_logic |

| 1 CH status bit out | |

| S_WILLIAM1_O | out std_logic |

| 1 CH status bit out | |

| S_HARRIS1_O | out std_logic |

| 1 CH status bit out | |

| S_HELMUT1_O | out std_logic |

| 1 CH status bit out | |

| S_IRENA2_O | out std_logic |

| 1 CH status bit out | |

| S_EWA2_O | out std_logic |

| 1 CH status bit out | |

| S_HEINZ2_O | out std_logic |

| 1 CH status bit out | |

| S_ANDREJ2_O | out std_logic |

| 1 CH status bit out | |

| S_MARKO2_O | out std_logic |

| 1 CH status bit out | |

| S_WILLIAM2_O | out std_logic |

| 1 CH status bit out | |

| S_HARRIS2_O | out std_logic |

| 1 CH status bit out | |

| S_HELMUT2_O | out std_logic |

| 1 CH status bit out | |

Detailed Description

narrow in-time time windowApplies in-time (collision) time-cut to 2 pulses per input channel. Passes inputs through with only in-time values enabled.

Definition at line 33 of file intime.vhd.

Member Data Documentation

ANDREJ1 in std_logic_vector ( 7 downto 0 ) [Port] |

ANDREJ1_O out std_logic_vector ( 7 downto 0 ) [Port] |

ANDREJ2 in std_logic_vector ( 7 downto 0 ) [Port] |

ANDREJ2_O out std_logic_vector ( 7 downto 0 ) [Port] |

CLK in std_logic [Port] |

EWA1 in std_logic_vector ( 7 downto 0 ) [Port] |

EWA1_O out std_logic_vector ( 7 downto 0 ) [Port] |

EWA2 in std_logic_vector ( 7 downto 0 ) [Port] |

EWA2_O out std_logic_vector ( 7 downto 0 ) [Port] |

HARRIS1 in std_logic_vector ( 7 downto 0 ) [Port] |

HARRIS1_O out std_logic_vector ( 7 downto 0 ) [Port] |

HARRIS2 in std_logic_vector ( 7 downto 0 ) [Port] |

HARRIS2_O out std_logic_vector ( 7 downto 0 ) [Port] |

HEINZ1 in std_logic_vector ( 7 downto 0 ) [Port] |

HEINZ1_O out std_logic_vector ( 7 downto 0 ) [Port] |

HEINZ2 in std_logic_vector ( 7 downto 0 ) [Port] |

HEINZ2_O out std_logic_vector ( 7 downto 0 ) [Port] |

HELMUT1 in std_logic_vector ( 7 downto 0 ) [Port] |

HELMUT1_O out std_logic_vector ( 7 downto 0 ) [Port] |

HELMUT2 in std_logic_vector ( 7 downto 0 ) [Port] |

HELMUT2_O out std_logic_vector ( 7 downto 0 ) [Port] |

ieee library [Library] |

IRENA1 in std_logic_vector ( 7 downto 0 ) [Port] |

IRENA1_O out std_logic_vector ( 7 downto 0 ) [Port] |

IRENA2 in std_logic_vector ( 7 downto 0 ) [Port] |

IRENA2_O out std_logic_vector ( 7 downto 0 ) [Port] |

LOWER_BOUND_A in std_logic_vector ( 5 downto 0 ) := " 010000 " [Port] |

LOWER_BOUND_C in std_logic_vector ( 5 downto 0 ) := " 010000 " [Port] |

MARKO1 in std_logic_vector ( 7 downto 0 ) [Port] |

MARKO1_O out std_logic_vector ( 7 downto 0 ) [Port] |

MARKO2 in std_logic_vector ( 7 downto 0 ) [Port] |

MARKO2_O out std_logic_vector ( 7 downto 0 ) [Port] |

S_ANDREJ1 in std_logic [Port] |

S_ANDREJ1_O out std_logic [Port] |

S_ANDREJ2 in std_logic [Port] |

S_ANDREJ2_O out std_logic [Port] |

S_EWA1 in std_logic [Port] |

S_EWA1_O out std_logic [Port] |

S_EWA2 in std_logic [Port] |

S_EWA2_O out std_logic [Port] |

S_HARRIS1 in std_logic [Port] |

S_HARRIS1_O out std_logic [Port] |

S_HARRIS2 in std_logic [Port] |

S_HARRIS2_O out std_logic [Port] |

S_HEINZ1 in std_logic [Port] |

S_HEINZ1_O out std_logic [Port] |

S_HEINZ2 in std_logic [Port] |

S_HEINZ2_O out std_logic [Port] |

S_HELMUT1 in std_logic [Port] |

S_HELMUT1_O out std_logic [Port] |

S_HELMUT2 in std_logic [Port] |

S_HELMUT2_O out std_logic [Port] |

S_IRENA1 in std_logic [Port] |

S_IRENA1_O out std_logic [Port] |

S_IRENA2 in std_logic [Port] |

S_IRENA2_O out std_logic [Port] |

S_MARKO1 in std_logic [Port] |

S_MARKO1_O out std_logic [Port] |

S_MARKO2 in std_logic [Port] |

S_MARKO2_O out std_logic [Port] |

S_WILLIAM1 in std_logic [Port] |

S_WILLIAM1_O out std_logic [Port] |

S_WILLIAM2 in std_logic [Port] |

S_WILLIAM2_O out std_logic [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 27 of file intime.vhd.

UPPER_BOUND_A in std_logic_vector ( 5 downto 0 ) := " 101110 " [Port] |

UPPER_BOUND_C in std_logic_vector ( 5 downto 0 ) := " 101110 " [Port] |

WILLIAM1 in std_logic_vector ( 7 downto 0 ) [Port] |

WILLIAM1_O out std_logic_vector ( 7 downto 0 ) [Port] |

WILLIAM2 in std_logic_vector ( 7 downto 0 ) [Port] |

WILLIAM2_O out std_logic_vector ( 7 downto 0 ) [Port] |

The documentation for this class was generated from the following file: