incrementer.incrementer_arc Architecture Reference

32-bit incrementer with synchronous reset and latched output More...

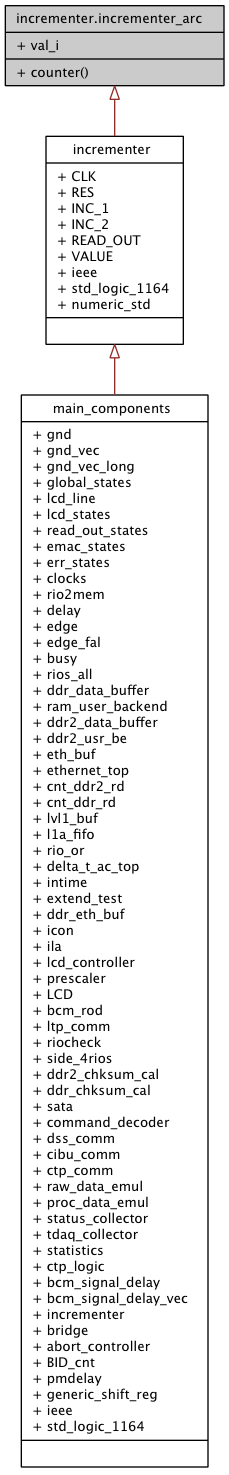

Inheritance diagram for incrementer.incrementer_arc:

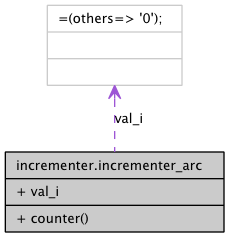

Collaboration diagram for incrementer.incrementer_arc:

Processes | |

| counter | ( CLK ) |

| incrementing counter | |

Signals | |

| val_i | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

Detailed Description

32-bit incrementer with synchronous reset and latched output32-bit incrementer with synchronous reset and latched output, reading the current counter value resets the counter. Increments can be by one, two or three.

Definition at line 50 of file incrementer.vhd.

Member Function Documentation

| counter | ( CLK ) |

incrementing counter

Definition at line 59 of file incrementer.vhd.

00059 counter : process (CLK) 00060 variable cnt : integer := 0; 00061 begin -- process counter 00062 if CLK'event and CLK = '1' then -- rising clock edge 00063 if RES = '1' then 00064 cnt := 0; 00065 val_i <= (others => '0'); 00066 else 00067 00068 if (INC_1 and INC_2) = '1' then 00069 cnt := cnt + 3; 00070 elsif INC_2 = '1' then 00071 cnt := cnt + 2; 00072 elsif INC_1 = '1' then 00073 cnt := cnt + 1; 00074 else 00075 cnt := cnt; 00076 end if; 00077 00078 if READ_OUT = '1' then 00079 val_i <= std_logic_vector(to_unsigned(cnt,32)); 00080 cnt := 0; 00081 else 00082 val_i <= val_i; 00083 end if; 00084 00085 end if; 00086 end if; 00087 end process counter;

The documentation for this class was generated from the following file: