eth_buf.eth_buf_arc Architecture Reference

address generation for buffer More...

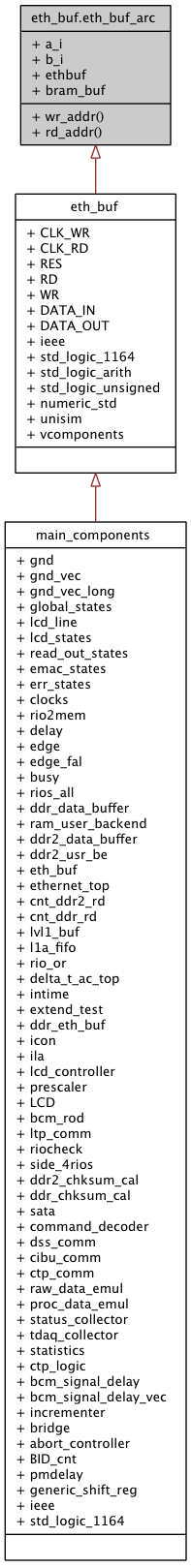

Inheritance diagram for eth_buf.eth_buf_arc:

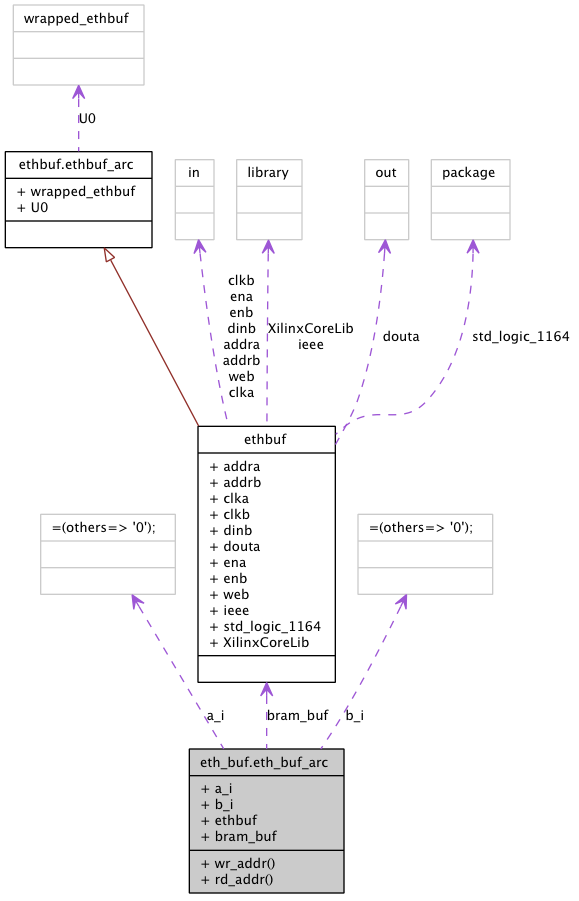

Collaboration diagram for eth_buf.eth_buf_arc:

Processes | |

| wr_addr | ( CLK_WR ) |

| write address generation | |

| rd_addr | ( CLK_RD ) |

| write address generation | |

Components | |

| ethbuf | <Entity ethbuf> |

| DPRAM. | |

Signals | |

| a_i | std_logic_vector ( 8 downto 0 ) := ( others = > ' 0 ' ) |

| b_i | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

Component Instantiations | |

| bram_buf | ethbuf <Entity ethbuf> |

Detailed Description

address generation for bufferDefinition at line 51 of file eth_buf.vhd.

Member Function Documentation

| rd_addr | ( CLK_RD ) |

write address generation

Definition at line 93 of file eth_buf.vhd.

00093 rd_addr : process(CLK_RD) 00094 begin 00095 if CLK_RD'event and CLK_RD = '1' then 00096 if RES = '1' then 00097 a_i <= (others => '0'); 00098 else 00099 if RD = '1' then 00100 if a_i = 383 then 00101 a_i <= (others => '0'); 00102 else 00103 a_i <= a_i + 1; 00104 end if; 00105 else 00106 a_i <= a_i; 00107 end if; 00108 end if; 00109 end if; 00110 end process rd_addr;

| wr_addr | ( CLK_WR ) |

write address generation

Definition at line 73 of file eth_buf.vhd.

00073 wr_addr : process(CLK_WR) 00074 begin 00075 if CLK_WR'event and CLK_WR = '1' then 00076 if RES = '1' then 00077 b_i <= conv_std_logic_vector(12, 5); 00078 else 00079 if WR = '1' then 00080 if b_i = 23 then 00081 b_i <= (others => '0'); 00082 else 00083 b_i <= b_i + 1; 00084 end if; 00085 else 00086 b_i <= b_i; 00087 end if; 00088 end if; 00089 end if; 00090 end process wr_addr;

Member Data Documentation

ethbuf [Component] |

The documentation for this class was generated from the following file: