ddr2_mem_wr_data_fifo_16.arc_wr_data_fifo_16 Architecture Reference

Write data FIFO. More...

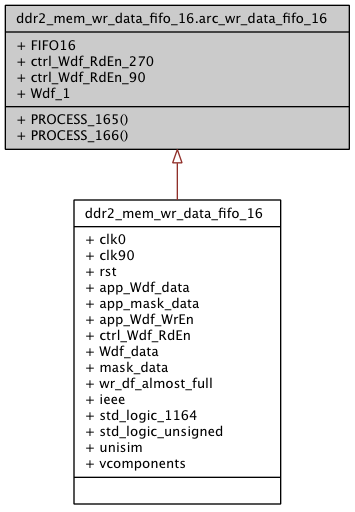

Inheritance diagram for ddr2_mem_wr_data_fifo_16.arc_wr_data_fifo_16:

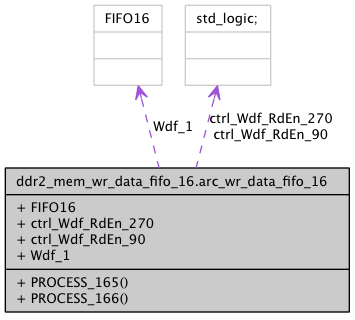

Collaboration diagram for ddr2_mem_wr_data_fifo_16.arc_wr_data_fifo_16:

Processes | |

| PROCESS_165 | ( clk90 ) |

| read enable sync | |

| PROCESS_166 | ( clk90 ) |

| read enable sync | |

Components | |

| FIFO16 | |

| FIFO primitive. | |

Signals | |

| ctrl_Wdf_RdEn_270 | std_logic |

| ctrl_Wdf_RdEn_90 | std_logic |

Component Instantiations | |

| Wdf_1 | FIFO16 |

| address FIFO | |

Detailed Description

Write data FIFO.This module instantiates the block RAM based FIFO to store the user interface data into it and read after a specified amount in already written. The reading starts when the almost full signal is generated whose offset is programmable.

Definition at line 78 of file ddr2_mem_wr_data_fifo_16.vhd.

Member Function Documentation

| PROCESS_165 | ( clk90 ) |

read enable sync

Definition at line 115 of file ddr2_mem_wr_data_fifo_16.vhd.

00115 process(clk90) 00116 begin 00117 if clk90'event and clk90 = '0' then 00118 ctrl_Wdf_RdEn_270 <= ctrl_Wdf_RdEn; 00119 end if; 00120 end process;

| PROCESS_166 | ( clk90 ) |

read enable sync

Definition at line 123 of file ddr2_mem_wr_data_fifo_16.vhd.

00123 process(clk90) 00124 begin 00125 if clk90'event and clk90 = '1' then 00126 ctrl_Wdf_RdEn_90 <= ctrl_Wdf_RdEn_270; 00127 end if; 00128 end process;

Member Data Documentation

FIFO16 [Component] |

The documentation for this class was generated from the following file: