ddr2_mem_wr_data_fifo_16 Entity Reference

Write data FIFO. More...

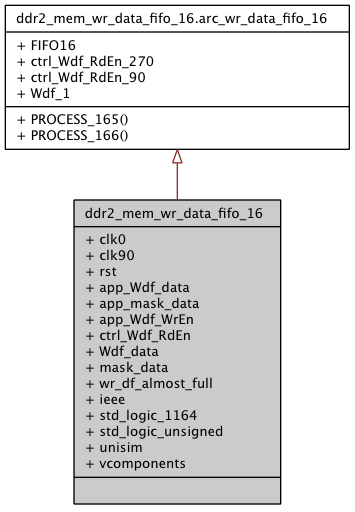

Inheritance diagram for ddr2_mem_wr_data_fifo_16:

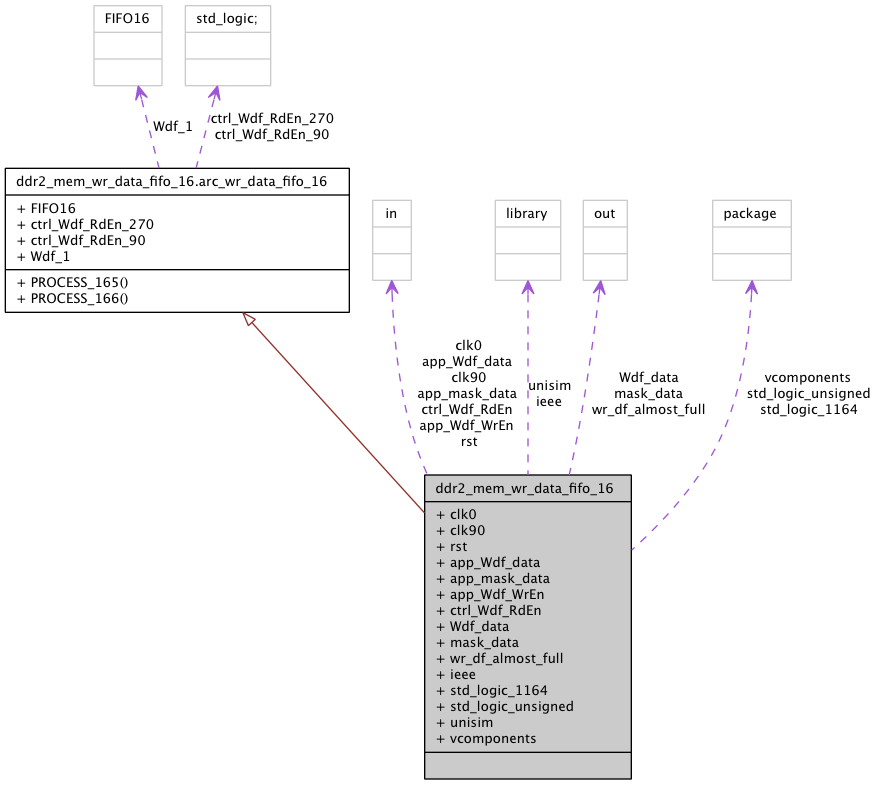

Collaboration diagram for ddr2_mem_wr_data_fifo_16:

Architectures | |

| arc_wr_data_fifo_16 | Architecture |

| Write data FIFO. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

| Library with Xilinx primitives. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| vcomponents | |

| Header with Xilinx primitives. | |

Ports | |

| clk0 | in std_logic |

| clk90 | in std_logic |

| rst | in std_logic |

| app_Wdf_data | in std_logic_vector ( 31 downto 0 ) |

| app_mask_data | in std_logic_vector ( 3 downto 0 ) |

| app_Wdf_WrEn | in std_logic |

| ctrl_Wdf_RdEn | in std_logic |

| Wdf_data | out std_logic_vector ( 31 downto 0 ) |

| mask_data | out std_logic_vector ( 3 downto 0 ) |

| wr_df_almost_full | out std_logic |

Detailed Description

Write data FIFO.This module instantiates the block RAM based FIFO to store the user interface data into it and read after a specified amount in already written. The reading starts when the almost full signal is generated whose offset is programmable.

Definition at line 58 of file ddr2_mem_wr_data_fifo_16.vhd.

Member Data Documentation

ieee library [Library] |

std_logic_1164 package [Package] |

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 47 of file ddr2_mem_wr_data_fifo_16.vhd.

unisim library [Library] |

vcomponents package [Package] |

The documentation for this class was generated from the following file: