ddr2_mem_v4_dqs_iob.arc_v4_dqs_iob Architecture Reference

DDR2 data strobe IOBs. More...

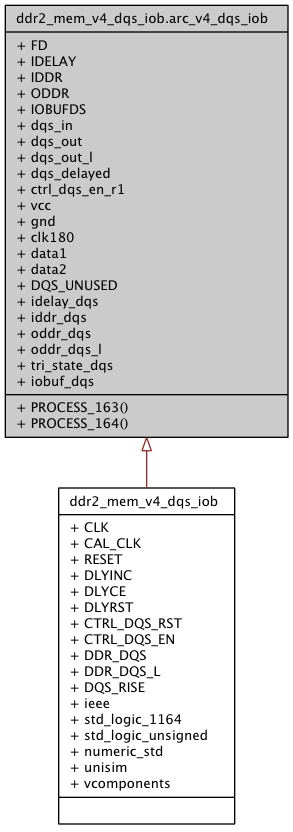

Inheritance diagram for ddr2_mem_v4_dqs_iob.arc_v4_dqs_iob:

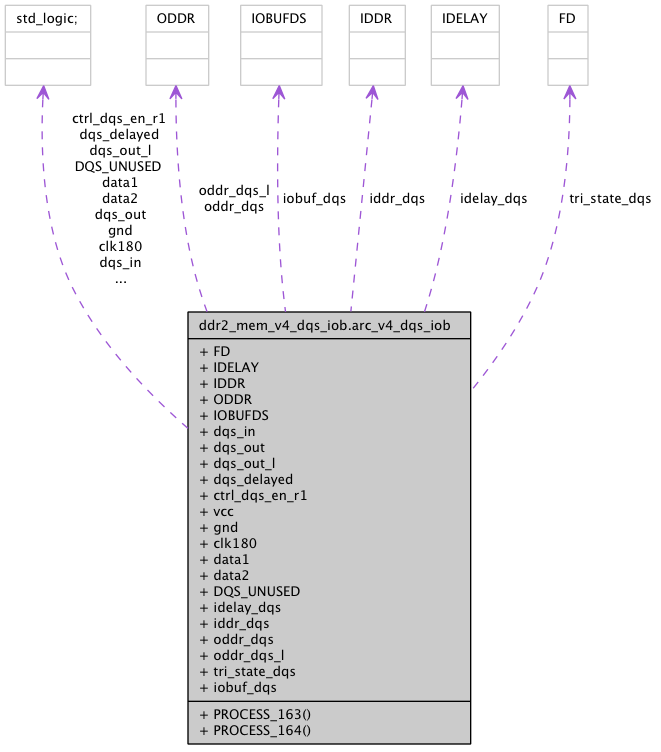

Collaboration diagram for ddr2_mem_v4_dqs_iob.arc_v4_dqs_iob:

Processes | |

| PROCESS_163 | ( clk180 ) |

| FF enable. | |

| PROCESS_164 | ( clk180 ) |

| FF enable. | |

Components | |

| FD | |

| D-FF primitive. | |

| IDELAY | |

| iDelay primitive | |

| IDDR | |

| DDR input buffer. | |

| ODDR | |

| DDR output buffer. | |

| IOBUFDS | |

| bidirectional IO-Buffer | |

Signals | |

| dqs_in | std_logic |

| dqs_out | std_logic |

| dqs_out_l | std_logic |

| dqs_delayed | std_logic |

| ctrl_dqs_en_r1 | std_logic |

| vcc | std_logic |

| gnd | std_logic |

| clk180 | std_logic |

| data1 | std_logic |

| data2 | std_logic |

| DQS_UNUSED | std_logic |

Component Instantiations | |

| idelay_dqs | IDELAY |

| iDelay instance | |

| iddr_dqs | IDDR |

| DDR input buffer. | |

| oddr_dqs | ODDR |

| DDR output buffer. | |

| oddr_dqs_l | ODDR |

| DDR output buffer. | |

| tri_state_dqs | FD |

| FF. | |

| iobuf_dqs | IOBUFDS |

| IO-Buffer. | |

Detailed Description

DDR2 data strobe IOBs.This module places the data stobes in the IOBs.

Definition at line 74 of file ddr2_mem_v4_dqs_iob.vhd.

Member Function Documentation

| PROCESS_163 | ( clk180 ) |

FF enable.

Definition at line 167 of file ddr2_mem_v4_dqs_iob.vhd.

00167 process(clk180) 00168 begin 00169 if clk180'event and clk180 = '1' then 00170 if (CTRL_DQS_RST = '1') then 00171 data1 <= '0'; 00172 else 00173 data1 <= '1'; 00174 end if; 00175 end if; 00176 end process;

| PROCESS_164 | ( clk180 ) |

FF enable.

Definition at line 179 of file ddr2_mem_v4_dqs_iob.vhd.

00179 process(clk180) 00180 begin 00181 if clk180'event and clk180 = '1' then 00182 if (CTRL_DQS_RST = '1') then 00183 data2 <= '1'; 00184 else 00185 data2 <= '0'; 00186 end if; 00187 end if; 00188 end process;

Member Data Documentation

FD [Component] |

IDDR [Component] |

IDELAY [Component] |

idelay_dqs IDELAY [Component Instantiation] |

IOBUFDS [Component] |

ODDR [Component] |

oddr_dqs_l ODDR [Component Instantiation] |

tri_state_dqs FD [Component Instantiation] |

The documentation for this class was generated from the following file: