ddr2_mem_rd_wr_addr_fifo_0.arc_rd_wr_addr_fifo Architecture Reference

FIFO for read/write address. More...

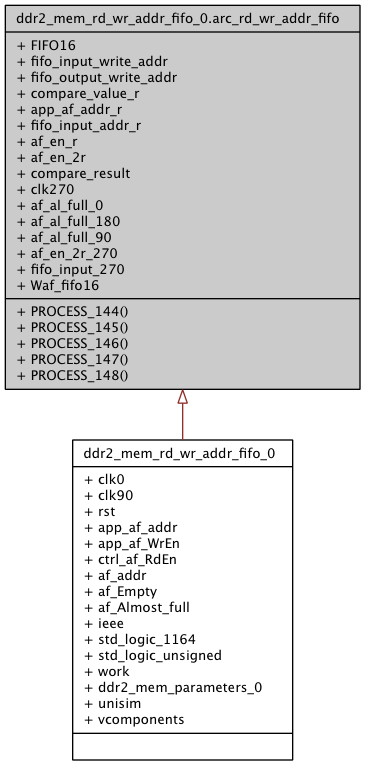

Inheritance diagram for ddr2_mem_rd_wr_addr_fifo_0.arc_rd_wr_addr_fifo:

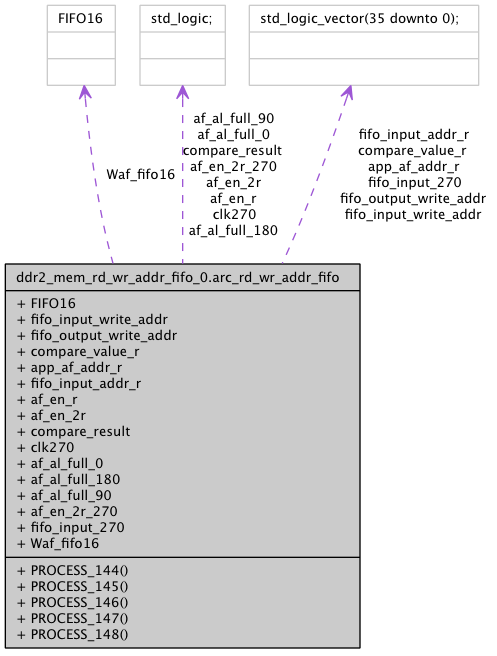

Collaboration diagram for ddr2_mem_rd_wr_addr_fifo_0.arc_rd_wr_addr_fifo:

Processes | |

| PROCESS_144 | ( clk0 ) |

| PROCESS_145 | ( clk270 ) |

| A fix for FIFO16 according to answer record #22462. | |

| PROCESS_146 | ( clk0 ) |

| 3 Filp-flops logic is implemented at output to avoid the timimg errors | |

| PROCESS_147 | ( clk90 ) |

| 3 Filp-flops logic is implemented at output to avoid the timimg errors | |

| PROCESS_148 | ( clk0 ) |

| 3 Filp-flops logic is implemented at output to avoid the timimg errors | |

Components | |

| FIFO16 | |

| FIFO primitive. | |

Signals | |

| fifo_input_write_addr | std_logic_vector ( 35 downto 0 ) |

| fifo_output_write_addr | std_logic_vector ( 35 downto 0 ) |

| compare_value_r | std_logic_vector ( 35 downto 0 ) |

| app_af_addr_r | std_logic_vector ( 35 downto 0 ) |

| fifo_input_addr_r | std_logic_vector ( 35 downto 0 ) |

| af_en_r | std_logic |

| af_en_2r | std_logic |

| compare_result | std_logic |

| clk270 | std_logic |

| af_al_full_0 | std_logic |

| af_al_full_180 | std_logic |

| af_al_full_90 | std_logic |

| af_en_2r_270 | std_logic |

| fifo_input_270 | std_logic_vector ( 35 downto 0 ) |

Component Instantiations | |

| Waf_fifo16 | FIFO16 |

| Address FIFO. | |

Detailed Description

FIFO for read/write address.This module instantiates the block RAM based FIFO to store the user address and the command information.

Definition at line 74 of file ddr2_mem_rd_wr_addr_fifo_0.vhd.

Member Function Documentation

| PROCESS_145 | ( clk270 ) |

A fix for FIFO16 according to answer record #22462.

Definition at line 151 of file ddr2_mem_rd_wr_addr_fifo_0.vhd.

00151 process(clk270) 00152 begin 00153 if (clk270'event and clk270 = '1') then 00154 af_en_2r_270 <= af_en_2r; 00155 fifo_input_270 <= fifo_input_addr_r; 00156 end if; 00157 end process;

| PROCESS_146 | ( clk0 ) |

3 Filp-flops logic is implemented at output to avoid the timimg errors

Definition at line 160 of file ddr2_mem_rd_wr_addr_fifo_0.vhd.

00160 process(clk0) 00161 begin 00162 if (clk0'event and clk0 = '0') then 00163 af_al_full_180 <= af_al_full_0; 00164 end if; 00165 end process;

| PROCESS_147 | ( clk90 ) |

3 Filp-flops logic is implemented at output to avoid the timimg errors

Definition at line 168 of file ddr2_mem_rd_wr_addr_fifo_0.vhd.

00168 process(clk90) 00169 begin 00170 if (clk90'event and clk90 = '1') then 00171 af_al_full_90 <= af_al_full_180; 00172 end if; 00173 end process;

| PROCESS_148 | ( clk0 ) |

3 Filp-flops logic is implemented at output to avoid the timimg errors

Definition at line 176 of file ddr2_mem_rd_wr_addr_fifo_0.vhd.

00176 process(clk0) 00177 begin 00178 if (clk0'event and clk0 = '1') then 00179 af_Almost_Full <= af_al_full_90; 00180 end if; 00181 end process;

Member Data Documentation

FIFO16 [Component] |

Waf_fifo16 FIFO16 [Component Instantiation] |

The documentation for this class was generated from the following file: