ddr2_mem_data_tap_inc.arc_data_tap_inc Architecture Reference

Tap logic. More...

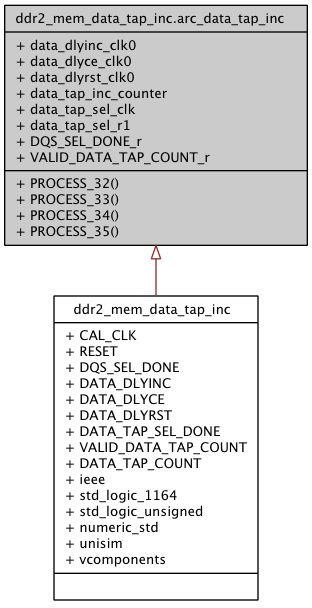

Inheritance diagram for ddr2_mem_data_tap_inc.arc_data_tap_inc:

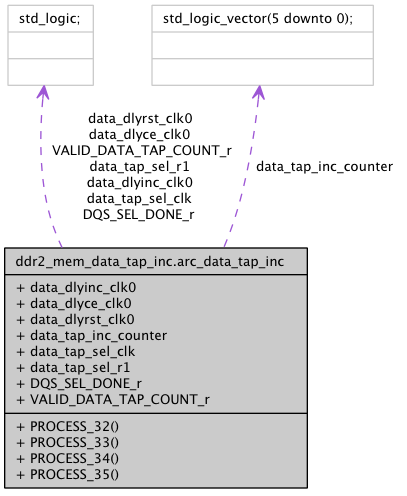

Collaboration diagram for ddr2_mem_data_tap_inc.arc_data_tap_inc:

Processes | |

| PROCESS_32 | ( CAL_CLK ) |

| done FF | |

| PROCESS_33 | ( CAL_CLK ) |

| select FF | |

| PROCESS_34 | ( CAL_CLK ) |

| valid FF | |

| PROCESS_35 | ( CAL_CLK ) |

| iDelay control logic | |

Signals | |

| data_dlyinc_clk0 | std_logic |

| data_dlyce_clk0 | std_logic |

| data_dlyrst_clk0 | std_logic |

| data_tap_inc_counter | std_logic_vector ( 5 downto 0 ) |

| data_tap_sel_clk | std_logic |

| data_tap_sel_r1 | std_logic |

| DQS_SEL_DONE_r | std_logic |

| VALID_DATA_TAP_COUNT_r | std_logic |

Detailed Description

Tap logic.The tap logic for calibration of the memory data with respect to FPGA clock is provided here. According to the edge detection or not the taps in the IDELAY element of the Virtex4 devices are either increased or decreased.

Definition at line 81 of file ddr2_mem_data_tap_inc.vhd.

Member Function Documentation

| PROCESS_32 | ( CAL_CLK ) |

done FF

Definition at line 100 of file ddr2_mem_data_tap_inc.vhd.

00100 process(CAL_CLK) 00101 begin 00102 if (CAL_CLK'event and CAL_CLK = '1') then 00103 if (RESET = '1') then 00104 DQS_SEL_DONE_r <= '0'; 00105 elsif(DQS_SEL_DONE = '1') then 00106 DQS_SEL_DONE_r <= '1'; 00107 else 00108 DQS_SEL_DONE_r <= DQS_SEL_DONE_r; 00109 end if; 00110 end if; 00111 end process;

| PROCESS_33 | ( CAL_CLK ) |

select FF

Definition at line 114 of file ddr2_mem_data_tap_inc.vhd.

00114 process(CAL_CLK) 00115 begin 00116 if (CAL_CLK'event and CAL_CLK = '1') then 00117 if (RESET = '1') then 00118 data_tap_sel_clk <= '0'; 00119 elsif (data_tap_inc_counter(5 downto 0) = "000001") then 00120 data_tap_sel_clk <= '1'; 00121 end if; 00122 end if; 00123 end process;

| PROCESS_34 | ( CAL_CLK ) |

valid FF

Definition at line 126 of file ddr2_mem_data_tap_inc.vhd.

00126 process(CAL_CLK) 00127 begin 00128 if (CAL_CLK'event and CAL_CLK = '1') then 00129 if (RESET = '1') then 00130 data_tap_sel_r1 <= '0'; 00131 VALID_DATA_TAP_COUNT_r <= '0'; 00132 else 00133 data_tap_sel_r1 <= data_tap_sel_clk; 00134 VALID_DATA_TAP_COUNT_r <= VALID_DATA_TAP_COUNT; 00135 end if; 00136 end if; 00137 end process;

| PROCESS_35 | ( CAL_CLK ) |

iDelay control logic

Definition at line 140 of file ddr2_mem_data_tap_inc.vhd.

00140 process(CAL_CLK) 00141 begin 00142 if (CAL_CLK'event and CAL_CLK = '1') then 00143 if (RESET = '1' or DQS_SEL_DONE_r = '0') then -- Data IDELAY in no change mode 00144 data_dlyinc_clk0 <= '0'; 00145 data_dlyce_clk0 <= '0'; 00146 data_dlyrst_clk0 <= '1'; 00147 data_tap_inc_counter(5 downto 0) <= "000000"; 00148 elsif (VALID_DATA_TAP_COUNT_r = '1') then 00149 data_dlyinc_clk0 <= '0'; 00150 data_dlyce_clk0 <= '0'; 00151 data_dlyrst_clk0 <= '0'; 00152 data_tap_inc_counter(5 downto 0) <= DATA_TAP_COUNT(5 downto 0); 00153 elsif (data_tap_inc_counter(5 downto 0) /= "000000") then -- Data IDELAY incremented 00154 data_dlyinc_clk0 <= '1'; 00155 data_dlyce_clk0 <= '1'; 00156 data_dlyrst_clk0 <= '0'; 00157 data_tap_inc_counter(5 downto 0) <= data_tap_inc_counter(5 downto 0) - "000001"; 00158 else -- Data IDELAY no change mode 00159 data_dlyinc_clk0 <= '0'; 00160 data_dlyce_clk0 <= '0'; 00161 data_dlyrst_clk0 <= '0'; 00162 data_tap_inc_counter(5 downto 0) <= "000000"; 00163 end if; 00164 end if; 00165 end process;

The documentation for this class was generated from the following file: