ddr2_mem_data_tap_inc Entity Reference

Tap logic. More...

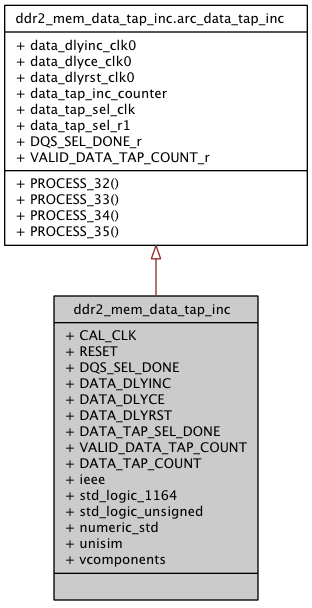

Inheritance diagram for ddr2_mem_data_tap_inc:

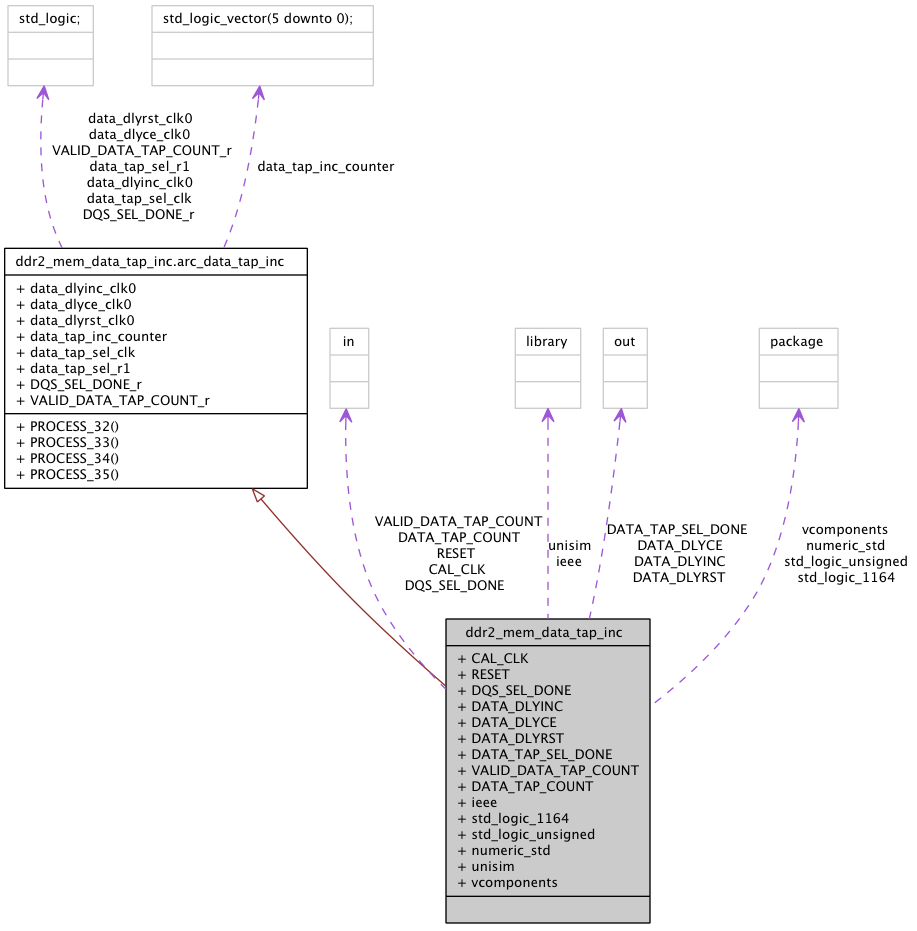

Collaboration diagram for ddr2_mem_data_tap_inc:

Architectures | |

| arc_data_tap_inc | Architecture |

| Tap logic. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| numeric_std | |

| arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file | |

| vcomponents | |

Ports | |

| CAL_CLK | in std_logic |

| calibration clock | |

| RESET | in std_logic |

| reset | |

| DQS_SEL_DONE | in std_logic |

| strobe select flag | |

| DATA_DLYINC | out std_logic |

| iDelay increment | |

| DATA_DLYCE | out std_logic |

| iDelay clock enable | |

| DATA_DLYRST | out std_logic |

| iDelay reset | |

| DATA_TAP_SEL_DONE | out std_logic |

| tap select | |

| VALID_DATA_TAP_COUNT | in std_logic |

| DATA_TAP_COUNT valid | |

| DATA_TAP_COUNT | in std_logic_vector ( 5 downto 0 ) |

| tap count | |

Detailed Description

Tap logic.The tap logic for calibration of the memory data with respect to FPGA clock is provided here. According to the edge detection or not the taps in the IDELAY element of the Virtex4 devices are either increased or decreased.

Definition at line 62 of file ddr2_mem_data_tap_inc.vhd.

Member Data Documentation

CAL_CLK in std_logic [Port] |

DATA_DLYCE out std_logic [Port] |

DATA_DLYINC out std_logic [Port] |

DATA_DLYRST out std_logic [Port] |

DATA_TAP_COUNT in std_logic_vector ( 5 downto 0 ) [Port] |

DATA_TAP_SEL_DONE out std_logic [Port] |

DQS_SEL_DONE in std_logic [Port] |

ieee library [Library] |

numeric_std package [Package] |

arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file

Definition at line 49 of file ddr2_mem_data_tap_inc.vhd.

RESET in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 47 of file ddr2_mem_data_tap_inc.vhd.

VALID_DATA_TAP_COUNT in std_logic [Port] |

The documentation for this class was generated from the following file: