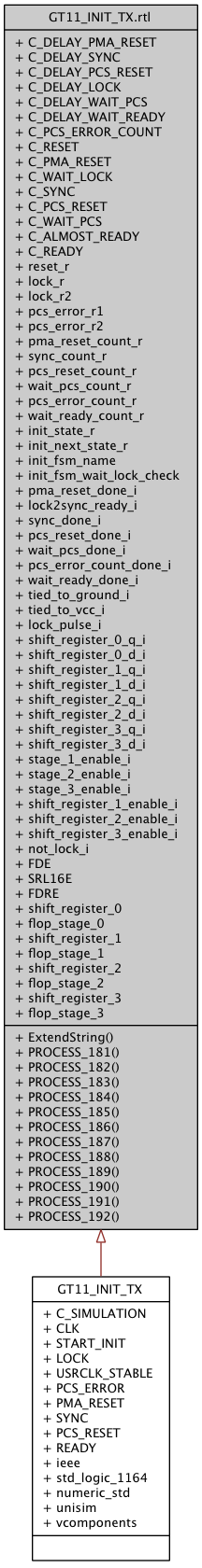

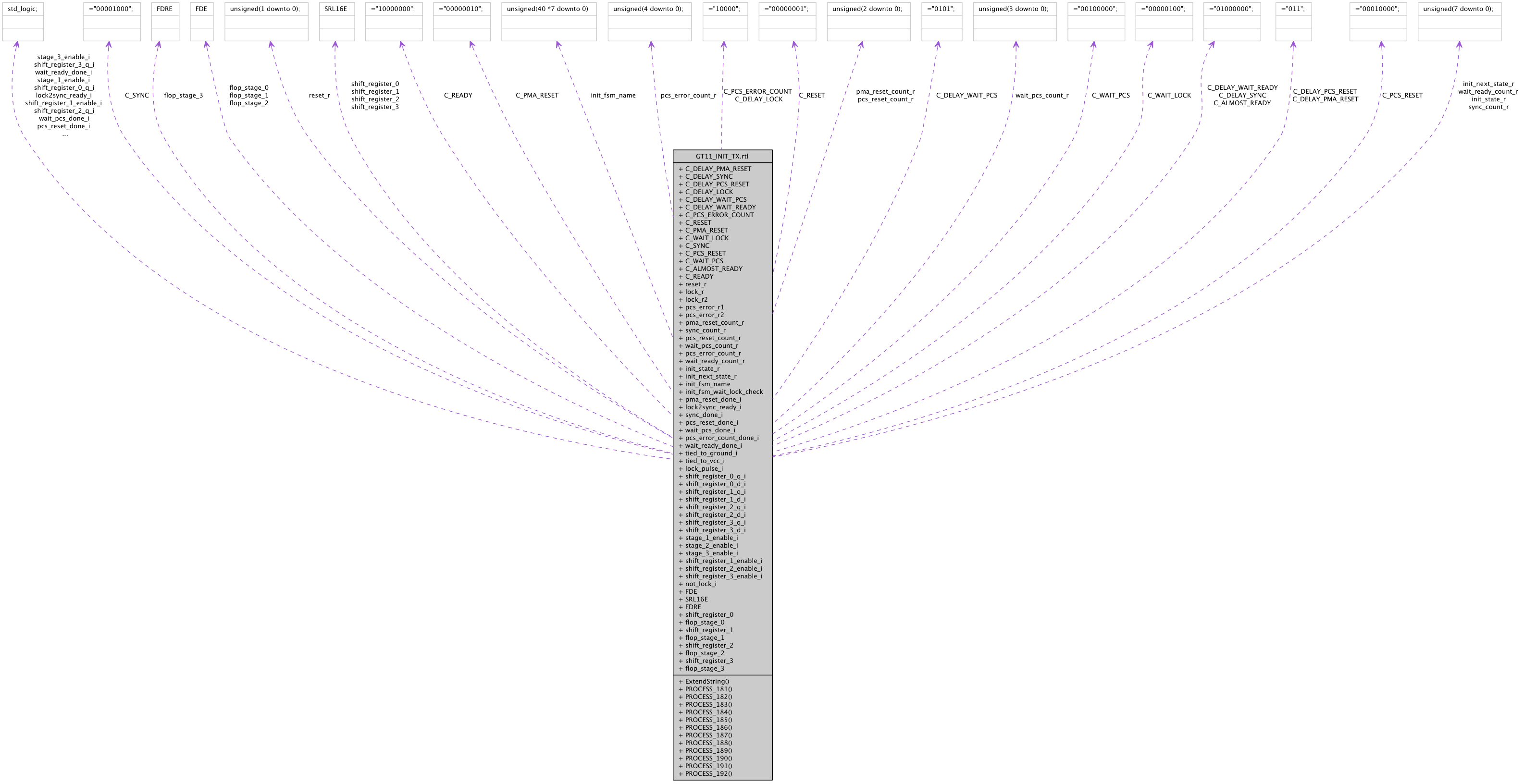

GT11_INIT_TX.rtl Architecture Reference

Initialization logic for RocketIO TX. More...

Functions | |

| string | ExtendString ( string_in: in string , string_len: in integer ) |

| extend a string | |

Processes | |

| PROCESS_181 | ( CLK , START_INIT ) |

| Synchronize START_INIT. | |

| PROCESS_182 | ( CLK ) |

| Synchronize LOCK. | |

| PROCESS_183 | ( CLK ) |

| Synchronize PCS_ERROR and generate a pulse when PCS error is high. | |

| PROCESS_184 | ( CLK ) |

| Counter for holding PMA reset for an amount of C_DELAY_PMA_RESET. | |

| PROCESS_185 | ( CLK ) |

| PROCESS_186 | ( CLK ) |

| Counter for holding SYNC for an amount of C_DELAY_SYNC. | |

| PROCESS_187 | ( CLK ) |

| Counter for holding PCS reset for an amount of C_DELAY_PCS_RESET. | |

| PROCESS_188 | ( CLK ) |

| Counter for waiting C_DELAY_WAIT_PCS after de-assertion of PCS reset. | |

| PROCESS_189 | ( CLK ) |

| Counter for PCS error. | |

| PROCESS_190 | ( CLK ) |

| Counter for the READY signal. | |

| PROCESS_191 | ( CLK ) |

| GT11 Initialization FSM reset. | |

| PROCESS_192 | ( reset_r(0) , pma_reset_done_i , init_fsm_wait_lock_check , lock_r , sync_done_i , pcs_reset_done_i , wait_pcs_done_i , pcs_error_r1 , pcs_error_count_done_i , wait_ready_done_i ) |

Components | |

| FDE | |

| component FDE | |

| SRL16E | |

| component SRL16 | |

| FDRE | |

| component FDRE | |

Constants | |

| C_DELAY_PMA_RESET | unsigned ( 2 downto 0 ) := " 011 " |

| 3 | |

| C_DELAY_SYNC | unsigned ( 7 downto 0 ) := " 01000000 " |

| 64 | |

| C_DELAY_PCS_RESET | unsigned ( 2 downto 0 ) := " 011 " |

| 3 | |

| C_DELAY_LOCK | unsigned ( 4 downto 0 ) := " 10000 " |

| 16 | |

| C_DELAY_WAIT_PCS | unsigned ( 3 downto 0 ) := " 0101 " |

| 5 | |

| C_DELAY_WAIT_READY | unsigned ( 7 downto 0 ) := " 01000000 " |

| 64 | |

| C_PCS_ERROR_COUNT | unsigned ( 4 downto 0 ) := " 10000 " |

| 16 | |

| C_RESET | unsigned ( 7 downto 0 ) := " 00000001 " |

| GT11 Initialization FSM state. | |

| C_PMA_RESET | unsigned ( 7 downto 0 ) := " 00000010 " |

| GT11 Initialization FSM state. | |

| C_WAIT_LOCK | unsigned ( 7 downto 0 ) := " 00000100 " |

| GT11 Initialization FSM state. | |

| C_SYNC | unsigned ( 7 downto 0 ) := " 00001000 " |

| GT11 Initialization FSM state. | |

| C_PCS_RESET | unsigned ( 7 downto 0 ) := " 00010000 " |

| GT11 Initialization FSM state. | |

| C_WAIT_PCS | unsigned ( 7 downto 0 ) := " 00100000 " |

| GT11 Initialization FSM state. | |

| C_ALMOST_READY | unsigned ( 7 downto 0 ) := " 01000000 " |

| GT11 Initialization FSM state. | |

| C_READY | unsigned ( 7 downto 0 ) := " 10000000 " |

| GT11 Initialization FSM state. | |

Signals | |

| reset_r | unsigned ( 1 downto 0 ) |

| lock_r | std_logic |

| lock_r2 | std_logic |

| pcs_error_r1 | std_logic |

| pcs_error_r2 | std_logic |

| pma_reset_count_r | unsigned ( 2 downto 0 ) |

| sync_count_r | unsigned ( 7 downto 0 ) |

| pcs_reset_count_r | unsigned ( 2 downto 0 ) |

| wait_pcs_count_r | unsigned ( 3 downto 0 ) |

| pcs_error_count_r | unsigned ( 4 downto 0 ) |

| wait_ready_count_r | unsigned ( 7 downto 0 ) |

| init_state_r | unsigned ( 7 downto 0 ) |

| init_next_state_r | unsigned ( 7 downto 0 ) |

| init_fsm_name | unsigned ( 40 *7 downto 0 ) |

| init_fsm_wait_lock_check | std_logic |

| pma_reset_done_i | std_logic |

| lock2sync_ready_i | std_logic |

| sync_done_i | std_logic |

| pcs_reset_done_i | std_logic |

| wait_pcs_done_i | std_logic |

| pcs_error_count_done_i | std_logic |

| wait_ready_done_i | std_logic |

| tied_to_ground_i | std_logic |

| tied_to_vcc_i | std_logic |

| lock_pulse_i | std_logic |

| shift_register_0_q_i | std_logic |

| shift_register_0_d_i | std_logic |

| shift_register_1_q_i | std_logic |

| shift_register_1_d_i | std_logic |

| shift_register_2_q_i | std_logic |

| shift_register_2_d_i | std_logic |

| shift_register_3_q_i | std_logic |

| shift_register_3_d_i | std_logic |

| stage_1_enable_i | std_logic |

| stage_2_enable_i | std_logic |

| stage_3_enable_i | std_logic |

| shift_register_1_enable_i | std_logic |

| shift_register_2_enable_i | std_logic |

| shift_register_3_enable_i | std_logic |

| not_lock_i | std_logic |

Component Instantiations | |

| shift_register_0 | SRL16E |

| flop_stage_0 | FDE |

| extra FF last stage | |

| shift_register_1 | SRL16E |

| SRL16 Stage One - Second stage of shifting. | |

| flop_stage_1 | FDE |

| extra FF last stage | |

| shift_register_2 | SRL16E |

| SRL16 Stage Two - Third stage of shifting. | |

| flop_stage_2 | FDE |

| extra FF last stage | |

| shift_register_3 | SRL16E |

| SRL16 Stage Three - Fourth stage of shifting. | |

| flop_stage_3 | FDRE |

| extra FF last stage | |

Detailed Description

Initialization logic for RocketIO TX.Definition at line 76 of file gt11_init_tx.vhd.

Member Function Documentation

| string ExtendString | ( string_in in string , | |

| string_len in integer ) |

extend a string

Definition at line 212 of file gt11_init_tx.vhd.

00212 function ExtendString (string_in : string; 00213 string_len : integer) 00214 return string is 00215 variable string_out : string(1 to string_len) := (others => ' '); 00216 00217 begin 00218 if string_in'length > string_len then 00219 string_out := string_in(1 to string_len); 00220 else 00221 string_out(1 to string_in'length) := string_in; 00222 end if; 00223 return string_out; 00224 end ExtendString;

| PROCESS_181 | ( CLK , | |

| START_INIT ) |

Synchronize START_INIT.

Definition at line 234 of file gt11_init_tx.vhd.

00234 process (CLK, START_INIT) 00235 begin 00236 if (START_INIT = '1') then 00237 reset_r <= "11"; 00238 elsif (rising_edge(CLK)) then 00239 reset_r <= '0' & reset_r(1); 00240 end if; 00241 end process;

| PROCESS_182 | ( CLK ) |

| PROCESS_183 | ( CLK ) |

Synchronize PCS_ERROR and generate a pulse when PCS error is high.

Definition at line 258 of file gt11_init_tx.vhd.

00258 process(CLK) 00259 begin 00260 if(CLK'event and CLK = '1') then 00261 if(reset_r(0) = '1') then 00262 pcs_error_r1 <= '0'; 00263 else 00264 pcs_error_r1 <= PCS_ERROR; 00265 end if; 00266 end if; 00267 end process;

| PROCESS_184 | ( CLK ) |

Counter for holding PMA reset for an amount of C_DELAY_PMA_RESET.

Definition at line 277 of file gt11_init_tx.vhd.

00277 process(CLK) 00278 begin 00279 if(CLK'event and CLK = '1') then 00280 if(init_state_r /= C_PMA_RESET) then 00281 pma_reset_count_r <= C_DELAY_PMA_RESET; 00282 else 00283 pma_reset_count_r <= pma_reset_count_r - 1; 00284 end if; 00285 end if; 00286 end process;

| PROCESS_185 | ( CLK ) |

Create a pulse from TXLOCK to initialize SRL16's. Need to register the LOCK signal from the GT11 twice since the LOCK is based on REFCLK

Definition at line 300 of file gt11_init_tx.vhd.

00300 process(CLK) 00301 begin 00302 if(CLK'event and CLK = '1') then 00303 if (reset_r(0) = '1') then 00304 lock_r2 <= '0'; 00305 else 00306 lock_r2 <= lock_r; 00307 end if; 00308 end if; 00309 end process;

| PROCESS_186 | ( CLK ) |

Counter for holding SYNC for an amount of C_DELAY_SYNC.

Definition at line 444 of file gt11_init_tx.vhd.

00444 process(CLK) 00445 begin 00446 if(CLK'event and CLK = '1') then 00447 if(init_state_r /= C_SYNC) then 00448 sync_count_r <= C_DELAY_SYNC; 00449 else 00450 sync_count_r <= sync_count_r - 1; 00451 end if; 00452 end if; 00453 end process;

| PROCESS_187 | ( CLK ) |

Counter for holding PCS reset for an amount of C_DELAY_PCS_RESET.

Definition at line 458 of file gt11_init_tx.vhd.

00458 process(CLK) 00459 begin 00460 if(CLK'event and CLK = '1') then 00461 if(init_state_r /= C_PCS_RESET) then 00462 pcs_reset_count_r <= C_DELAY_PCS_RESET; 00463 else 00464 pcs_reset_count_r <= pcs_reset_count_r - 1; 00465 end if; 00466 end if; 00467 end process;

| PROCESS_188 | ( CLK ) |

Counter for waiting C_DELAY_WAIT_PCS after de-assertion of PCS reset.

Definition at line 472 of file gt11_init_tx.vhd.

00472 process(CLK) 00473 begin 00474 if(CLK'event and CLK = '1') then 00475 if(init_state_r /= C_WAIT_PCS) then 00476 wait_pcs_count_r <= C_DELAY_WAIT_PCS; 00477 else 00478 wait_pcs_count_r <= wait_pcs_count_r - 1; 00479 end if; 00480 end if; 00481 end process;

| PROCESS_189 | ( CLK ) |

Counter for PCS error.

Definition at line 486 of file gt11_init_tx.vhd.

00486 process(CLK) 00487 begin 00488 if(CLK'event and CLK = '1') then 00489 if(init_state_r = C_PMA_RESET) then 00490 pcs_error_count_r <= C_PCS_ERROR_COUNT; 00491 elsif (((init_state_r = C_ALMOST_READY) or (init_state_r = C_READY)) and (pcs_error_r1 and lock_r) = '1') then 00492 pcs_error_count_r <= pcs_error_count_r - 1; 00493 end if; 00494 end if; 00495 end process;

| PROCESS_190 | ( CLK ) |

Counter for the READY signal.

Definition at line 500 of file gt11_init_tx.vhd.

00500 process(CLK) 00501 begin 00502 if(CLK'event and CLK = '1') then 00503 if((init_state_r /= C_ALMOST_READY) or (pcs_error_r1 = '1')) then 00504 wait_ready_count_r <= C_DELAY_WAIT_READY; 00505 elsif(pcs_error_r1 = '0') then 00506 wait_ready_count_r <= wait_ready_count_r - 1; 00507 end if; 00508 end if; 00509 end process;

| PROCESS_191 | ( CLK ) |

GT11 Initialization FSM reset.

Definition at line 514 of file gt11_init_tx.vhd.

00514 process (CLK) 00515 begin 00516 if (rising_edge(CLK)) then 00517 if (reset_r(0) = '1') then 00518 init_state_r <= C_RESET; 00519 else 00520 init_state_r <= init_next_state_r; 00521 end if; 00522 end if; 00523 end process;

| PROCESS_192 | ( reset_r(0) , | |

| pma_reset_done_i , | ||

| init_fsm_wait_lock_check , | ||

| lock_r , | ||

| sync_done_i , | ||

| pcs_reset_done_i , | ||

| wait_pcs_done_i , | ||

| pcs_error_r1 , | ||

| pcs_error_count_done_i , | ||

| wait_ready_done_i ) |

GT11 Initialization FSM - This FSM is used to initialize the GT11 block asserting the PMA and PCS reset in sequence. It also takes into account of any error that may happen during initialization. The block uses USRCLK as reference for the delay. DO NOT use the output of the GT11 clocks for this reset module, as the output clocks may change when reset is applied to the GT11. Use a system clock, and make sure that the wait time for each state equals the specified number of USRCLK cycles.

The following steps are applied:

- C_RESET: Upon system reset of this block, PMA reset will be asserted

- C_PMA_RESET: PMA reset is held for 3 USRCLK cycles

- C_WAIT_LOCK: Wait for LOCK. After LOCK is asserted, wait for 12,000 USRCLK2 cycles and wait for the USRCLK of the GT11s to be stable before going to the next state to assert the PCS reset. If LOCK gets de-asserted, we reset the counter and wait for LOCK again.

- C_SYNC: Assert SYNG for 64 SYNC cycles. If LOCK gets de-asserted, we go back to Step 3.

- C_PCS_RESET: Assert PCS reset for 3 USRCLK cycles. If LOCK gets de-asserted, we go back to Step 3.

- C_WAIT_PCS: After de-assertion of PCS reset, wait 5 USRCLK cycles. If LOCK gets de-asserted, we go back to Step 3.

- C_ALMOST_READY: Go to the Almost Ready state. If LOCK gets de-asserted, we go back to Step 3. If there is a PCS error (i.e. buffer error) detected while LOCK is high, we go back to Step 4. If we cycle PCS reset for an N number of C_PCS_ERROR_COUNT, we go back to Step 1 to do a PMA reset.

- C_READY: Go to the Ready state. We reach this state after waiting 64 USRCLK cycles without any PCS errors. We assert the READY signal to denote that this block finishes initializing the GT11. If there is a PCS error during this state, we go back to Step 4. If LOCK is lost, we go back to Step 3.

Definition at line 558 of file gt11_init_tx.vhd.

00558 process (reset_r(0), pma_reset_done_i, init_fsm_wait_lock_check, lock_r, 00559 sync_done_i, pcs_reset_done_i, wait_pcs_done_i, pcs_error_r1, 00560 pcs_error_count_done_i, wait_ready_done_i) 00561 variable init_fsm_name : string(1 to 25); 00562 begin 00563 case init_state_r is 00564 00565 when C_RESET => 00566 00567 if (reset_r(0) = '1') then 00568 init_next_state_r <= C_RESET; 00569 else 00570 init_next_state_r <= C_PMA_RESET; 00571 end if; 00572 init_fsm_name := ExtendString("C_RESET", 25); 00573 00574 when C_PMA_RESET => 00575 00576 if (pma_reset_done_i = '1') then 00577 init_next_state_r <= C_WAIT_LOCK; 00578 else 00579 init_next_state_r <= C_PMA_RESET; 00580 end if; 00581 init_fsm_name := ExtendString("C_PMA_RESET", 25); 00582 00583 when C_WAIT_LOCK => 00584 00585 if(init_fsm_wait_lock_check = '1') then 00586 init_next_state_r <= C_SYNC; 00587 else 00588 init_next_state_r <= C_WAIT_LOCK; 00589 end if; 00590 init_fsm_name := ExtendString("C_WAIT_LOCK", 25); 00591 00592 when C_SYNC => 00593 if (lock_r = '1') then 00594 if (sync_done_i = '1') then 00595 init_next_state_r <= C_PCS_RESET; 00596 else 00597 init_next_state_r <= C_SYNC; 00598 end if; 00599 else 00600 init_next_state_r <= C_WAIT_LOCK; 00601 end if; 00602 init_fsm_name := ExtendString("C_SYNC", 25); 00603 00604 when C_PCS_RESET => 00605 if (lock_r = '1') then 00606 if (pcs_reset_done_i = '1') then 00607 init_next_state_r <= C_WAIT_PCS; 00608 else 00609 init_next_state_r <= C_PCS_RESET; 00610 end if; 00611 else 00612 init_next_state_r <= C_WAIT_LOCK; 00613 end if; 00614 init_fsm_name := ExtendString("C_PCS_RESET", 25); 00615 00616 when C_WAIT_PCS => 00617 if (lock_r = '1') then 00618 if (wait_pcs_done_i = '1') then 00619 init_next_state_r <= C_ALMOST_READY; 00620 else 00621 init_next_state_r <= C_WAIT_PCS; 00622 end if; 00623 else 00624 init_next_state_r <= C_WAIT_LOCK; 00625 end if; 00626 init_fsm_name := ExtendString("C_WAIT_PCS", 25); 00627 00628 when C_ALMOST_READY => 00629 if (lock_r = '0') then 00630 init_next_state_r <= C_WAIT_LOCK; 00631 elsif ((pcs_error_r1 = '1') and (pcs_error_count_done_i = '0')) then 00632 init_next_state_r <= C_SYNC; 00633 elsif ((pcs_error_r1 = '1') and (pcs_error_count_done_i = '1')) then 00634 init_next_state_r <= C_PMA_RESET; 00635 elsif (wait_ready_done_i = '1') then 00636 init_next_state_r <= C_READY; 00637 else 00638 init_next_state_r <= C_ALMOST_READY; 00639 end if; 00640 init_fsm_name := ExtendString("C_ALMOST_READY", 25); 00641 00642 when C_READY => 00643 if ((lock_r = '1') and (pcs_error_r1 = '0')) then 00644 init_next_state_r <= C_READY; 00645 elsif ((lock_r = '1') and (pcs_error_r1 = '1')) then 00646 init_next_state_r <= C_PCS_RESET; 00647 else 00648 init_next_state_r <= C_WAIT_LOCK; 00649 end if; 00650 init_fsm_name := ExtendString("C_READY", 25); 00651 00652 when others => 00653 init_next_state_r <= C_RESET; 00654 init_fsm_name := ExtendString("C_RESET", 25); 00655 00656 end case; 00657 end process;

Member Data Documentation

C_ALMOST_READY unsigned ( 7 downto 0 ) := " 01000000 " [Constant] |

C_DELAY_LOCK unsigned ( 4 downto 0 ) := " 10000 " [Constant] |

C_DELAY_PCS_RESET unsigned ( 2 downto 0 ) := " 011 " [Constant] |

C_DELAY_PMA_RESET unsigned ( 2 downto 0 ) := " 011 " [Constant] |

C_DELAY_SYNC unsigned ( 7 downto 0 ) := " 01000000 " [Constant] |

C_DELAY_WAIT_PCS unsigned ( 3 downto 0 ) := " 0101 " [Constant] |

C_DELAY_WAIT_READY unsigned ( 7 downto 0 ) := " 01000000 " [Constant] |

C_PCS_ERROR_COUNT unsigned ( 4 downto 0 ) := " 10000 " [Constant] |

C_PCS_RESET unsigned ( 7 downto 0 ) := " 00010000 " [Constant] |

C_PMA_RESET unsigned ( 7 downto 0 ) := " 00000010 " [Constant] |

C_READY unsigned ( 7 downto 0 ) := " 10000000 " [Constant] |

C_RESET unsigned ( 7 downto 0 ) := " 00000001 " [Constant] |

C_SYNC unsigned ( 7 downto 0 ) := " 00001000 " [Constant] |

C_WAIT_LOCK unsigned ( 7 downto 0 ) := " 00000100 " [Constant] |

C_WAIT_PCS unsigned ( 7 downto 0 ) := " 00100000 " [Constant] |

FDE [Component] |

FDRE [Component] |

flop_stage_0 FDE [Component Instantiation] |

flop_stage_1 FDE [Component Instantiation] |

flop_stage_2 FDE [Component Instantiation] |

flop_stage_3 FDRE [Component Instantiation] |

shift_register_0 SRL16E [Component Instantiation] |

Counter for the wait time between assertion of TXLOCK and assertion to TXSYNC cycles. There is a requirement of 12,000 TXUSRCLK2 cycles between these two points. Please refer to the reset section of the User Guide for more information. This is built with SRL16s. In this module, we assume 1 USRCLK2 = 1 USRCLK (please adjust the address of the fourth SRL16 stage as neccessary). The whole four stages give 12,288 cycles of delay (16 * 16 * 16 * 3); note that the last stage has an extra FF at the end.

Definition at line 324 of file gt11_init_tx.vhd.

shift_register_1 SRL16E [Component Instantiation] |

shift_register_2 SRL16E [Component Instantiation] |

shift_register_3 SRL16E [Component Instantiation] |

SRL16E [Component] |

The documentation for this class was generated from the following file: