sata_GT11_INIT_RX Entity Reference

RIO-RX initializer. More...

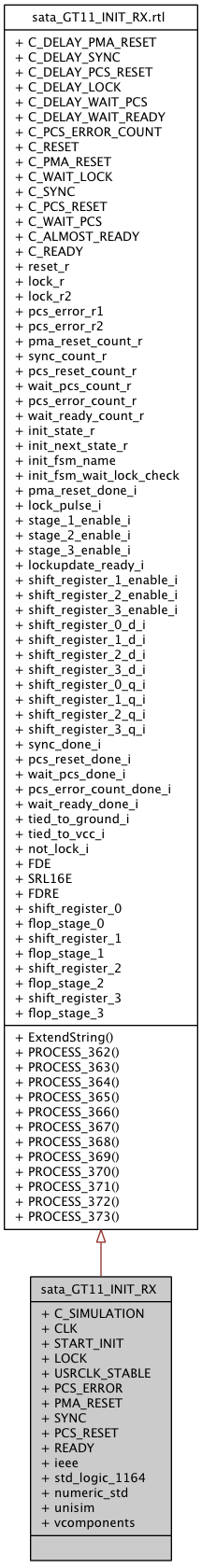

Inheritance diagram for sata_GT11_INIT_RX:

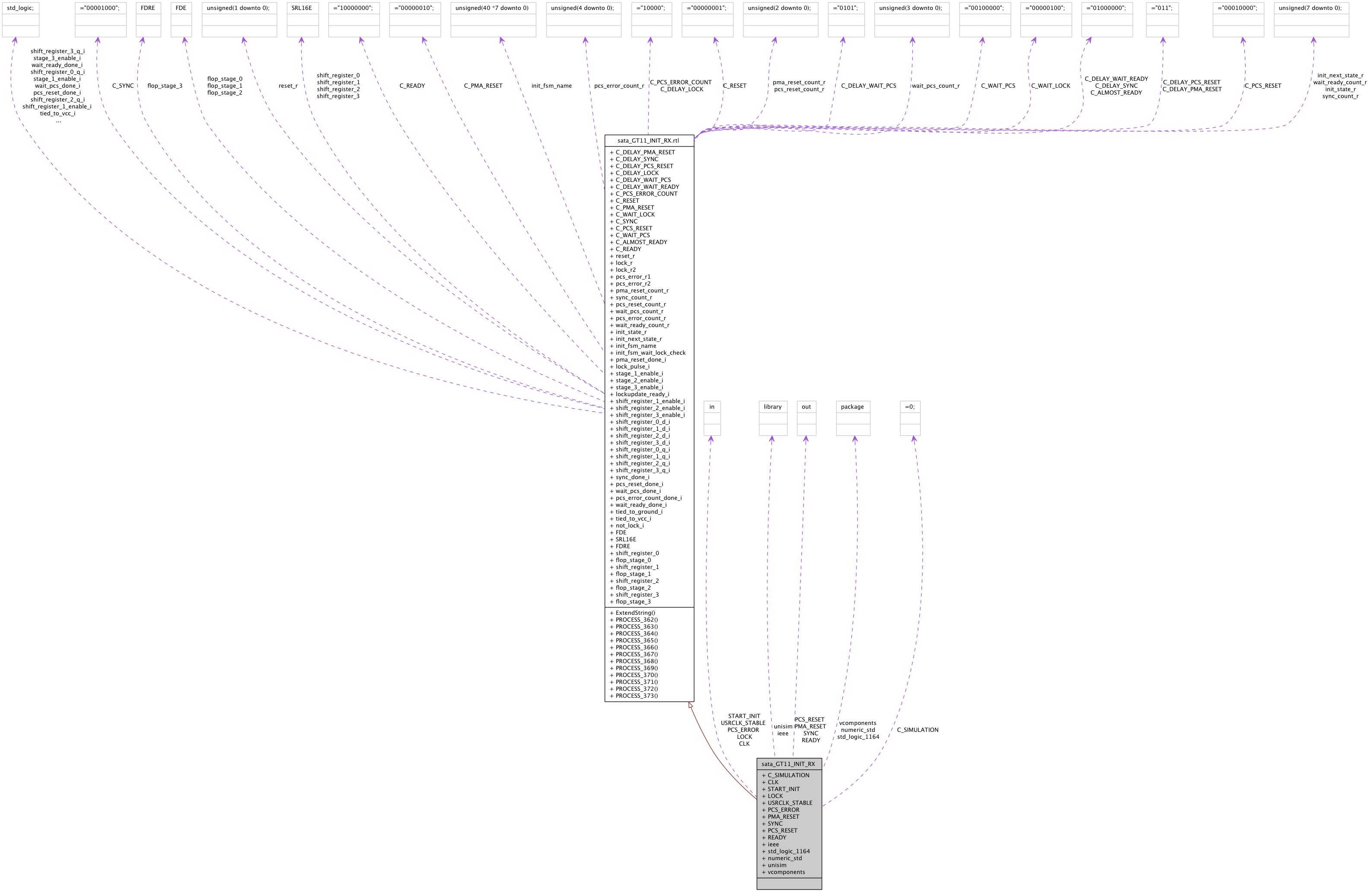

Collaboration diagram for sata_GT11_INIT_RX:

Architectures | |

| rtl | Architecture |

| RIO-RX initializer. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

| Library with Xilinx primitives. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| numeric_std | |

| arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file | |

| vcomponents | |

| Header with Xilinx primitives. | |

Generics | |

| C_SIMULATION | integer := 0 |

| Set to 1 for simulation. | |

Ports | |

| CLK | in std_logic |

| clock | |

| START_INIT | in std_logic |

| trigger initialization | |

| LOCK | in std_logic |

| lock flag | |

| USRCLK_STABLE | in std_logic |

| clock stable flag | |

| PCS_ERROR | in std_logic |

| pcs error flag | |

| PMA_RESET | out std_logic |

| pma reset | |

| SYNC | out std_logic |

| sync | |

| PCS_RESET | out std_logic |

| pcs reset | |

| READY | out std_logic |

| ready flag | |

Detailed Description

RIO-RX initializer.this entity produces signal sequences for initializing rio rx

Definition at line 59 of file sata_gt11_init_rx.vhd.

Member Data Documentation

C_SIMULATION integer := 0 [Generic] |

CLK in std_logic [Port] |

ieee library [Library] |

LOCK in std_logic [Port] |

numeric_std package [Package] |

arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file

Definition at line 47 of file sata_gt11_init_rx.vhd.

PCS_ERROR in std_logic [Port] |

PCS_RESET out std_logic [Port] |

PMA_RESET out std_logic [Port] |

READY out std_logic [Port] |

START_INIT in std_logic [Port] |

std_logic_1164 package [Package] |

SYNC out std_logic [Port] |

unisim library [Library] |

USRCLK_STABLE in std_logic [Port] |

vcomponents package [Package] |

The documentation for this class was generated from the following file: