onescompaccu Entity Reference

Accu with Carry Look-Ahead Adder. More...

Inheritance diagram for onescompaccu:

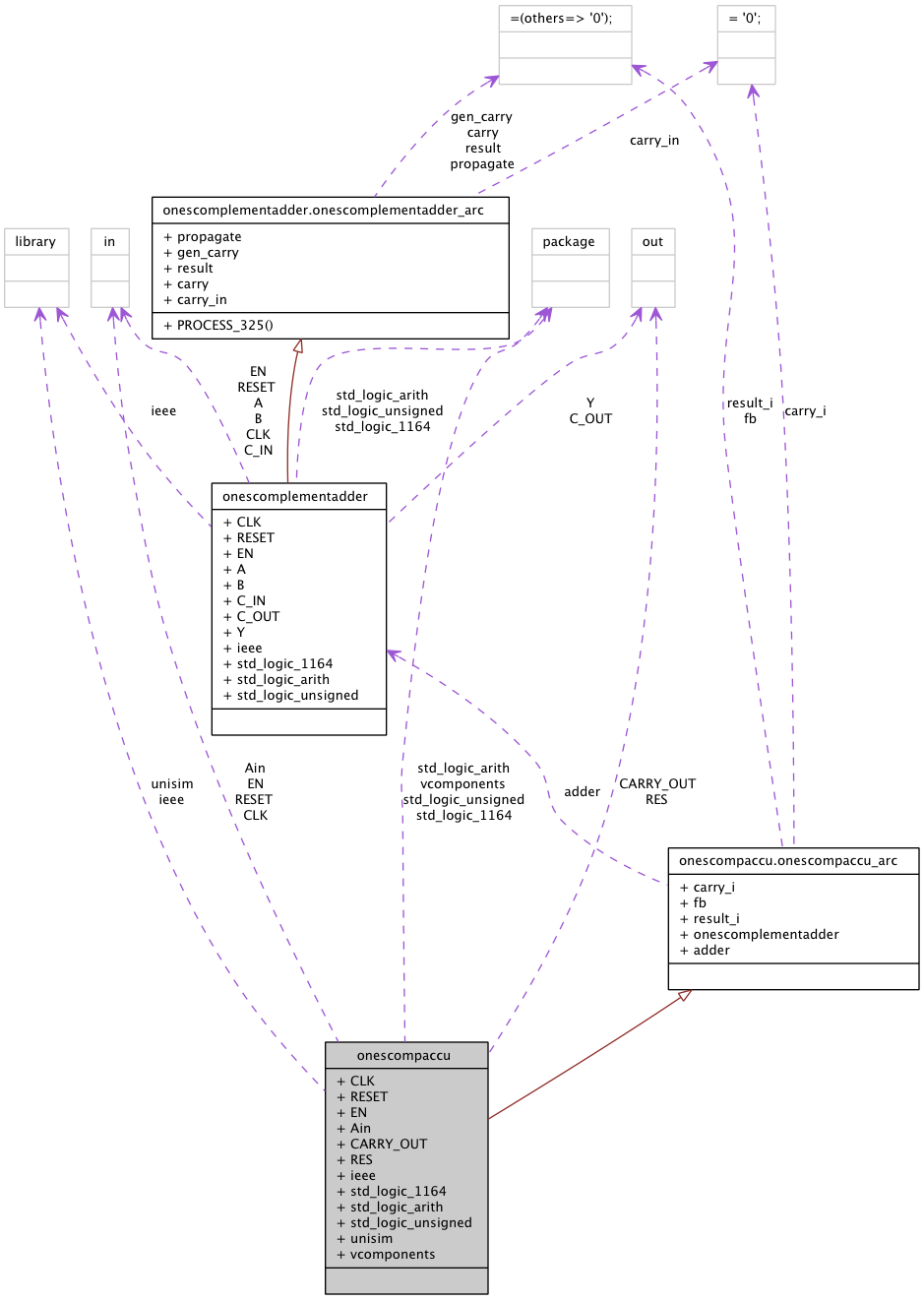

Collaboration diagram for onescompaccu:

Architectures | |

| onescompaccu_arc | Architecture |

| logic around CLA-Adder More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

| Library with Xilinx primitives. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| vcomponents | |

| Header with Xilinx primitives. | |

Ports | |

| CLK | in std_logic |

| Clock. | |

| RESET | in std_logic |

| Reset. | |

| EN | in std_logic |

| Enable. | |

| Ain | in std_logic_vector ( 15 downto 0 ) |

| Data in. | |

| CARRY_OUT | out std_logic |

| Carry output. | |

| RES | out std_logic_vector ( 15 downto 0 ) |

| Output value. | |

Detailed Description

Accu with Carry Look-Ahead Adder.Wrapper file for CLA-Adder with feedback to turn it into an accumulator

Definition at line 39 of file onescompaccu.vhd.

Member Data Documentation

Ain in std_logic_vector ( 15 downto 0 ) [Port] |

CARRY_OUT out std_logic [Port] |

CLK in std_logic [Port] |

EN in std_logic [Port] |

ieee library [Library] |

RES out std_logic_vector ( 15 downto 0 ) [Port] |

RESET in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 28 of file onescompaccu.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file onescompaccu.vhd.

unisim library [Library] |

vcomponents package [Package] |

The documentation for this class was generated from the following file: