mem_interface_top_idelay_ctrl Entity Reference

Virtex-4 IDELAYCTRL Wrapper. More...

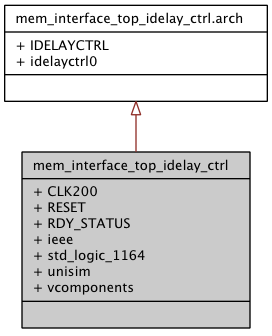

Inheritance diagram for mem_interface_top_idelay_ctrl:

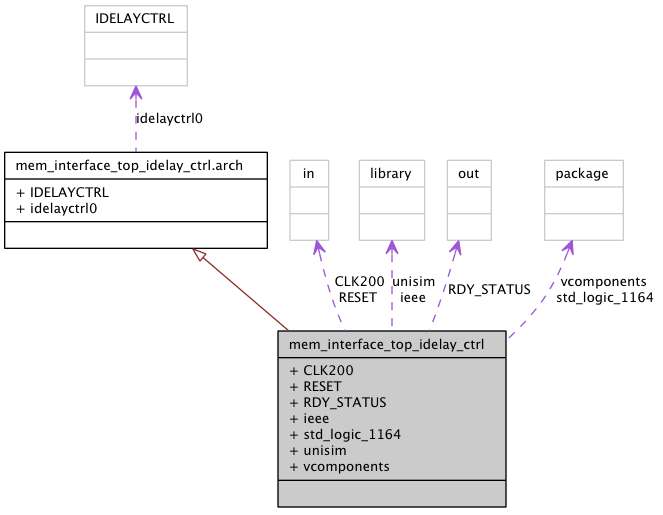

Collaboration diagram for mem_interface_top_idelay_ctrl:

Architectures | |

| arch | Architecture |

| Virtex-4 IDELAYCTRL Wrapper. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

| Library with Xilinx primitives. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| vcomponents | |

| Header with Xilinx primitives. | |

Ports | |

| CLK200 | in std_logic |

| 200 MHz clock in | |

| RESET | in std_logic |

| Reset. | |

| RDY_STATUS | out std_logic |

| Status flag. | |

Detailed Description

Virtex-4 IDELAYCTRL Wrapper.Instantiates the IDELAYCTRL primitive of the Virtex4 device which continously calibrates the IDELAY elements in the region in case of varying operating conditions. It takes a 200MHz clock as an input.

Definition at line 53 of file mem_interface_top_idelay_ctrl.vhd.

Member Data Documentation

CLK200 in std_logic [Port] |

ieee library [Library] |

RDY_STATUS out std_logic [Port] |

RESET in std_logic [Port] |

std_logic_1164 package [Package] |

unisim library [Library] |

vcomponents package [Package] |

The documentation for this class was generated from the following file: