ddr_data_buffer.ddr_data_buffer_arc Architecture Reference

interface between DAQ & DDR More...

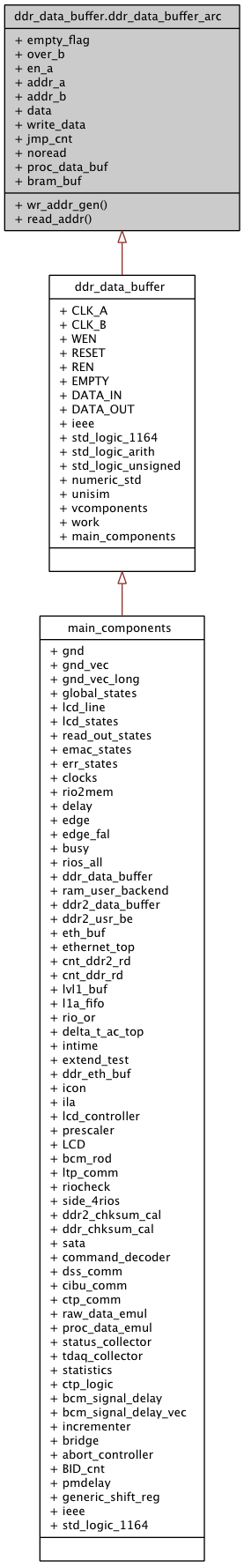

Inheritance diagram for ddr_data_buffer.ddr_data_buffer_arc:

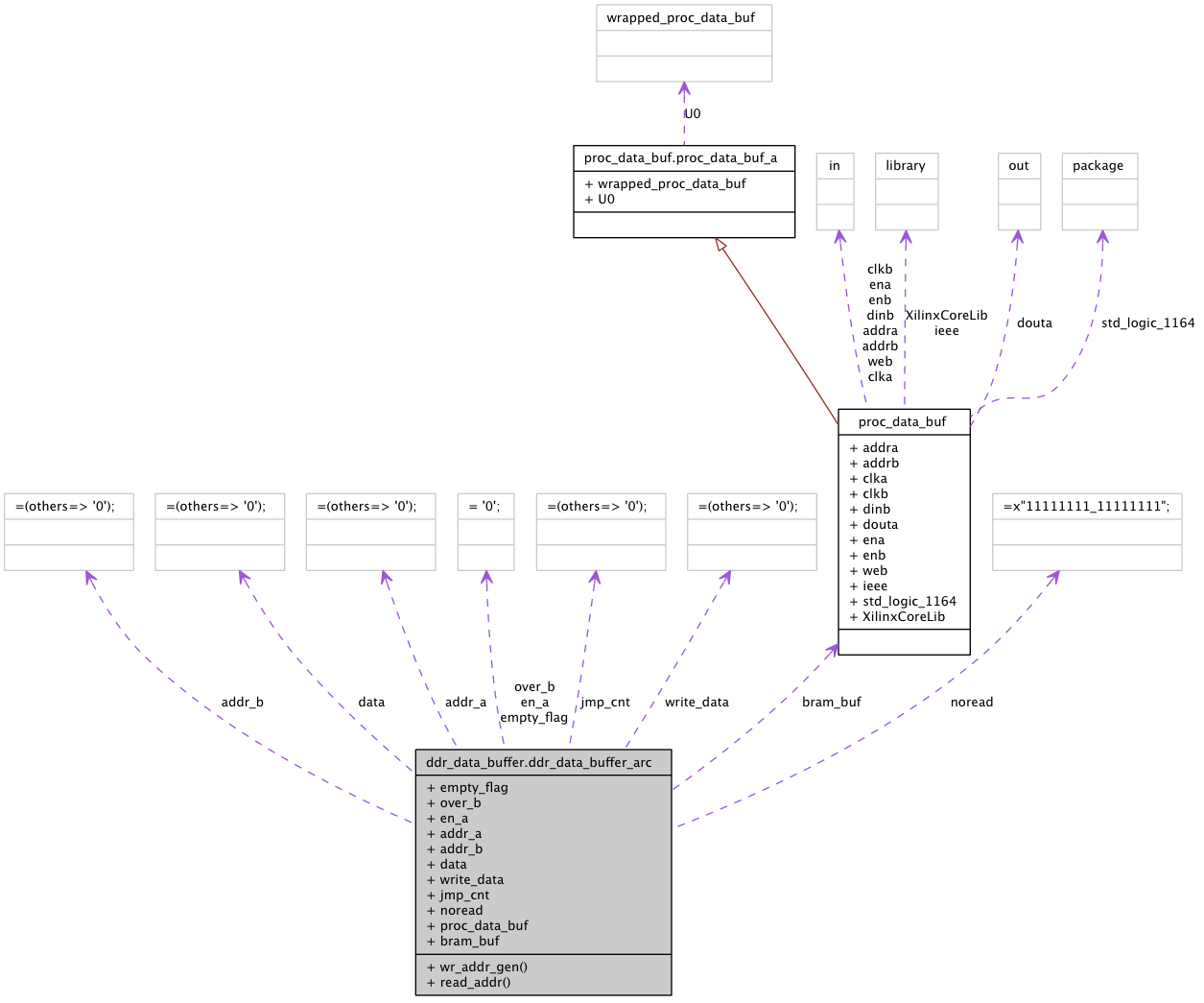

Collaboration diagram for ddr_data_buffer.ddr_data_buffer_arc:

Processes | |

| wr_addr_gen | ( CLK_B ) |

| Write address generation. | |

| read_addr | ( CLK_A ) |

| read address generation, steps over reserved fields | |

Components | |

| proc_data_buf | <Entity proc_data_buf> |

| wrapped DPBRAM | |

Constants | |

| noread | std_logic_vector ( 63 downto 0 ) := x " 11111111_11111111 " |

| filler for reserved fields | |

Signals | |

| empty_flag | std_logic := ' 0 ' |

| over_b | std_logic := ' 0 ' |

| en_a | std_logic := ' 0 ' |

| addr_a | std_logic_vector ( 8 downto 0 ) := ( others = > ' 0 ' ) |

| addr_b | std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

| data | std_logic_vector ( 63 downto 0 ) := ( others = > ' 0 ' ) |

| write_data | std_logic_vector ( 255 downto 0 ) := ( others = > ' 0 ' ) |

| jmp_cnt | std_logic_vector ( 1 downto 0 ) := ( others = > ' 0 ' ) |

Component Instantiations | |

| bram_buf | proc_data_buf <Entity proc_data_buf> |

| DPBRAM buffer. | |

Detailed Description

interface between DAQ & DDRDefinition at line 55 of file ddr_data_buffer.vhd.

Member Function Documentation

| read_addr | ( clk_a ) |

read address generation, steps over reserved fields

Definition at line 129 of file ddr_data_buffer.vhd.

00129 read_addr : process(clk_a) 00130 begin 00131 if clk_a'event and clk_a = '1' then 00132 if RESET = '1' then 00133 addr_a <= (others => '0'); 00134 jmp_cnt <= (others => '0'); 00135 else 00136 if REN = '1' then 00137 if jmp_cnt = 2 then 00138 addr_a <= addr_a + 2; 00139 jmp_cnt <= (others => '0'); 00140 else 00141 jmp_cnt <= jmp_cnt + 1; 00142 addr_a <= addr_a + 1; 00143 end if; 00144 else 00145 addr_a <= addr_a; 00146 end if; 00147 end if; 00148 end if; 00149 end process read_addr;

| wr_addr_gen | ( clk_b ) |

Write address generation.

Definition at line 106 of file ddr_data_buffer.vhd.

00106 wr_addr_gen : process(clk_b) 00107 begin 00108 if clk_b'event and clk_b = '1' then 00109 if RESET = '1' then 00110 addr_b <= (others => '0'); 00111 over_b <= '0'; 00112 else 00113 if WEN = '1' then 00114 addr_b <= addr_b + 1; 00115 if addr_b = "1111110" then 00116 over_b <= '1'; 00117 end if; 00118 else 00119 addr_b <= addr_b; 00120 end if; 00121 end if; 00122 end if; 00123 end process wr_addr_gen;

Member Data Documentation

bram_buf proc_data_buf [Component Instantiation] |

noread std_logic_vector ( 63 downto 0 ) := x " 11111111_11111111 " [Constant] |

proc_data_buf [Component] |

The documentation for this class was generated from the following file: