cal_block_v1_4_1 Entity Reference

RocketIO calibration module. More...

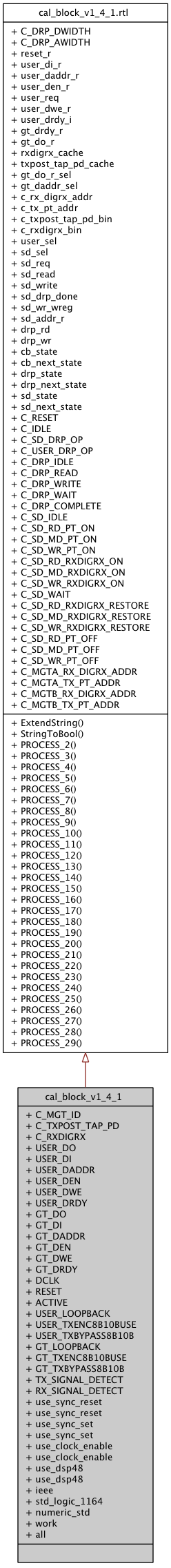

Inheritance diagram for cal_block_v1_4_1:

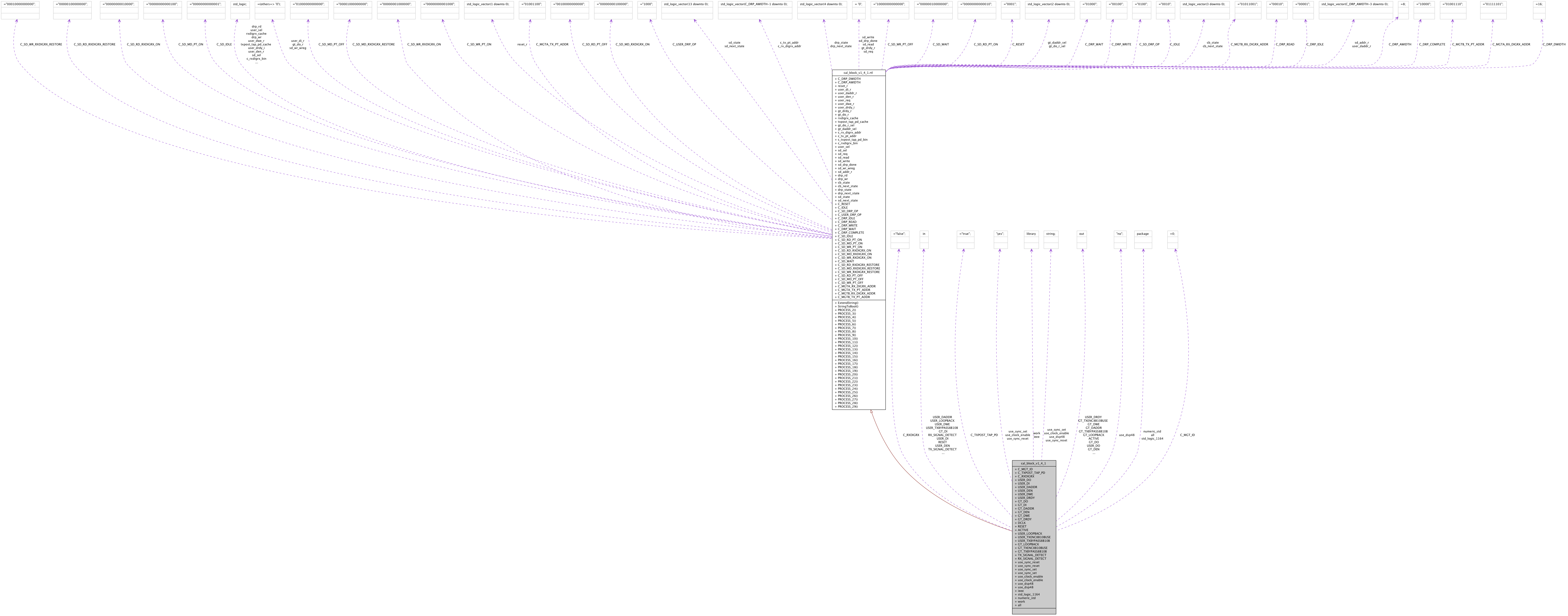

Collaboration diagram for cal_block_v1_4_1:

Architectures | |

| rtl | Architecture |

| RocketIO calibration module. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| work | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| numeric_std | |

| arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file | |

| all | |

Generics | |

| C_MGT_ID | integer := 0 |

| 0 = MGTA | 1 = MGTB | |

| C_TXPOST_TAP_PD | string := " true " |

| Default POST TAP PD. | |

| C_RXDIGRX | string := " false " |

| Default RXDIGRX. | |

Ports | |

| USER_DO | out std_logic_vector ( 16-1 downto 0 ) |

| DRP data out. | |

| USER_DI | in std_logic_vector ( 16-1 downto 0 ) |

| DRP data in. | |

| USER_DADDR | in std_logic_vector ( 8-1 downto 0 ) |

| DRP address. | |

| USER_DEN | in std_logic |

| DRP enable. | |

| USER_DWE | in std_logic |

| DRP write enable. | |

| USER_DRDY | out std_logic |

| DRP ready flag. | |

| GT_DO | out std_logic_vector ( 16-1 downto 0 ) |

| MGT data out. | |

| GT_DI | in std_logic_vector ( 16-1 downto 0 ) |

| MGT data in. | |

| GT_DADDR | out std_logic_vector ( 8-1 downto 0 ) |

| MGT address. | |

| GT_DEN | out std_logic |

| MGT enable. | |

| GT_DWE | out std_logic |

| MGT write enable. | |

| GT_DRDY | in std_logic |

| MGT ready flag. | |

| DCLK | in std_logic |

| DRP clock. | |

| RESET | in std_logic |

| Reset. | |

| ACTIVE | out std_logic |

| active flag for backwards compatibility | |

| USER_LOOPBACK | in std_logic_vector ( 1 downto 0 ) |

| MGT loopback. | |

| USER_TXENC8B10BUSE | in std_logic |

| 8b10b encoding flag | |

| USER_TXBYPASS8B10B | in std_logic_vector ( 7 downto 0 ) |

| 8b10b bypass | |

| GT_LOOPBACK | out std_logic_vector ( 1 downto 0 ) |

| MGT loopback. | |

| GT_TXENC8B10BUSE | out std_logic |

| 8b10b encoding flag | |

| GT_TXBYPASS8B10B | out std_logic_vector ( 7 downto 0 ) |

| 8b10b bypass | |

| TX_SIGNAL_DETECT | in std_logic |

| TX detect. | |

| RX_SIGNAL_DETECT | in std_logic |

| RX detect. | |

Attributes | |

| use_sync_reset | string |

| synchronous reset | |

| use_sync_reset | " yes " |

| use_sync_set | string |

| synchronous set | |

| use_sync_set | " yes " |

| use_clock_enable | string |

| clock enable | |

| use_clock_enable | " yes " |

| use_dsp48 | string |

| inhibit DSP48 inference | |

| use_dsp48 | " no " |

Detailed Description

RocketIO calibration module.created by RocketIO wizard

Definition at line 86 of file cal_block_v1_4_1.vhd.

Member Data Documentation

ACTIVE out std_logic [Port] |

C_MGT_ID integer := 0 [Generic] |

C_RXDIGRX string := " false " [Generic] |

C_TXPOST_TAP_PD string := " true " [Generic] |

DCLK in std_logic [Port] |

GT_DADDR out std_logic_vector ( 8-1 downto 0 ) [Port] |

GT_DEN out std_logic [Port] |

GT_DI in std_logic_vector ( 16-1 downto 0 ) [Port] |

GT_DO out std_logic_vector ( 16-1 downto 0 ) [Port] |

GT_DRDY in std_logic [Port] |

GT_DWE out std_logic [Port] |

GT_LOOPBACK out std_logic_vector ( 1 downto 0 ) [Port] |

GT_TXBYPASS8B10B out std_logic_vector ( 7 downto 0 ) [Port] |

GT_TXENC8B10BUSE out std_logic [Port] |

ieee library [Library] |

numeric_std package [Package] |

arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file

Definition at line 79 of file cal_block_v1_4_1.vhd.

RESET in std_logic [Port] |

RX_SIGNAL_DETECT in std_logic [Port] |

std_logic_1164 package [Package] |

TX_SIGNAL_DETECT in std_logic [Port] |

use_clock_enable string [Attribute] |

use_dsp48 string [Attribute] |

use_sync_reset string [Attribute] |

use_sync_set string [Attribute] |

USER_DADDR in std_logic_vector ( 8-1 downto 0 ) [Port] |

USER_DEN in std_logic [Port] |

USER_DI in std_logic_vector ( 16-1 downto 0 ) [Port] |

USER_DO out std_logic_vector ( 16-1 downto 0 ) [Port] |

USER_DRDY out std_logic [Port] |

USER_DWE in std_logic [Port] |

USER_LOOPBACK in std_logic_vector ( 1 downto 0 ) [Port] |

USER_TXBYPASS8B10B in std_logic_vector ( 7 downto 0 ) [Port] |

USER_TXENC8B10BUSE in std_logic [Port] |

The documentation for this class was generated from the following file: