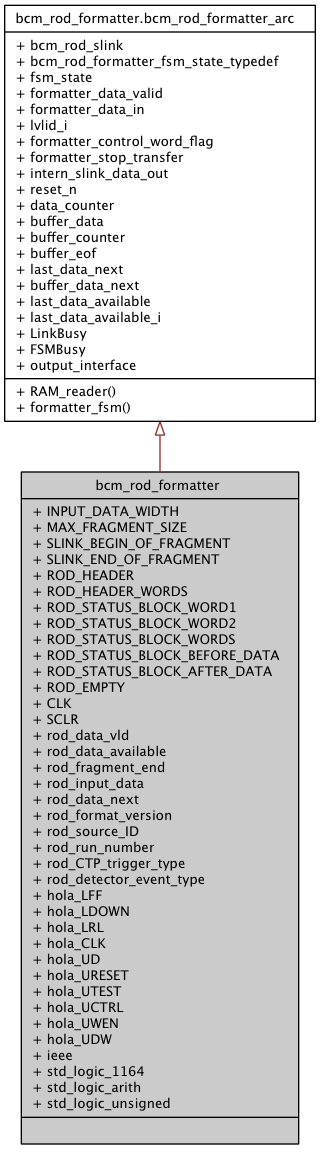

bcm_rod_formatter Entity Reference

ROD formatter. More...

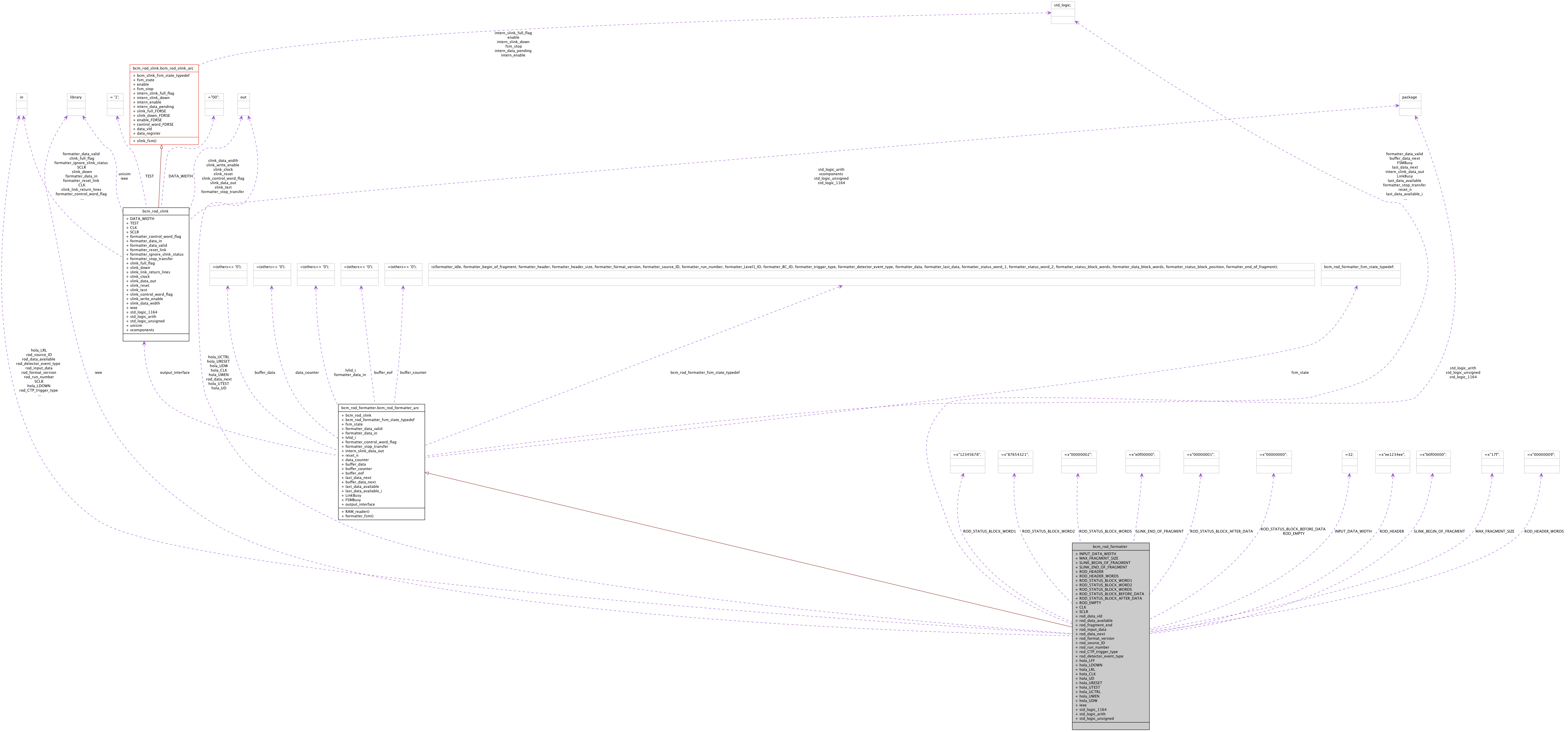

Architectures | |

| bcm_rod_formatter_arc | Architecture |

| ROD formatter main FSM. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

Generics | |

| INPUT_DATA_WIDTH | positive := 32 |

| data width | |

| MAX_FRAGMENT_SIZE | std_logic_vector ( 11 downto 0 ) := x " 17f " |

| reaching maximum of (64*6)-1=383 words | |

| SLINK_BEGIN_OF_FRAGMENT | std_logic_vector ( 31 downto 0 ) := x " b0f00000 " |

| magic number constant | |

| SLINK_END_OF_FRAGMENT | std_logic_vector ( 31 downto 0 ) := x " e0f00000 " |

| magic number constant | |

| ROD_HEADER | std_logic_vector ( 31 downto 0 ) := x " ee1234ee " |

| magic number constant | |

| ROD_HEADER_WORDS | std_logic_vector ( 31 downto 0 ) := x " 00000009 " |

| magic number constant | |

| ROD_STATUS_BLOCK_WORD1 | std_logic_vector ( 31 downto 0 ) := x " 12345678 " |

| magic number constant | |

| ROD_STATUS_BLOCK_WORD2 | std_logic_vector ( 31 downto 0 ) := x " 87654321 " |

| magic number constant | |

| ROD_STATUS_BLOCK_WORDS | std_logic_vector ( 31 downto 0 ) := x " 00000002 " |

| magic number constant | |

| ROD_STATUS_BLOCK_BEFORE_DATA | std_logic_vector ( 31 downto 0 ) := x " 00000000 " |

| magic number constant | |

| ROD_STATUS_BLOCK_AFTER_DATA | std_logic_vector ( 31 downto 0 ) := x " 00000001 " |

| magic number constant | |

| ROD_EMPTY | std_logic_vector ( 31 downto 0 ) := x " 00000000 " |

| magic number constant | |

Ports | |

| CLK | in std_logic |

| 40 MHz clock | |

| SCLR | in std_logic |

| synchronous clear (reset) signal | |

| rod_data_vld | in std_logic |

| indicates data is valid | |

| rod_data_available | in std_logic := ' 0 ' |

| indicates data is available | |

| rod_fragment_end | in std_logic := ' 0 ' |

| indicates end of fragment | |

| rod_input_data | in std_logic_vector ( INPUT_DATA_WIDTH -1 downto 0 ) |

| input data | |

| rod_data_next | out std_logic := ' 0 ' |

| fetch next data blob | |

| rod_format_version | in std_logic_vector ( 31 downto 0 ) := x " 03010001 " |

| ROD format version. | |

| rod_source_ID | in std_logic_vector ( 31 downto 0 ) := x " 00810000 " |

| source ID | |

| rod_run_number | in std_logic_vector ( 31 downto 0 ) := x " 7fffffff " |

| run number | |

| rod_CTP_trigger_type | in std_logic_vector ( 31 downto 0 ) := x " 00000011 " |

| Level-1 trigger type. | |

| rod_detector_event_type | in std_logic_vector ( 31 downto 0 ) := x " 000000dd " |

| detector event type | |

| hola_LFF | in std_logic |

| SLINK full flag (LFF) !!! ACTIVE LOW !!! | |

| hola_LDOWN | in std_logic |

| SLINK down (LDOWN) !!! ACTIVE LOW !!! | |

| hola_LRL | in std_logic_vector ( 3 downto 0 ) |

| SLINK return data lines (LRL) !!! NOT USED !!! | |

| hola_CLK | out std_logic |

| SLINK clock (UCLK). | |

| hola_UD | out std_logic_vector ( 31 downto 0 ) |

| SLINK data output (UD). | |

| hola_URESET | out std_logic |

| SLINK reset link (URESET) !!! ACTIVE LOW !!! | |

| hola_UTEST | out std_logic |

| SLINK test line (UTEST) !!! ACTIVE LOW !!! | |

| hola_UCTRL | out std_logic |

| SLINK control word flag (UCTRL) !!! ACTIVE LOW !!! | |

| hola_UWEN | out std_logic |

| SLINK write enable (UWEN) !!! ACTIVE LOW !!! | |

| hola_UDW | out std_logic_vector ( 1 downto 0 ) := " 00 " |

| SLINK data width (UDW) "00"=32-bit, "01"=16-bit, "10"=8-bit, "11"=reserved. | |

Detailed Description

ROD formatter.

main ROD formatter module. Assembles the packets by reading data in the right order from the ROD RAM and shifting it along according to the current state of the FSM, which steps through the ATLAS raw event format (specification can be found on EDMS.

Detailed description of the ROD formatter is available here.

Definition at line 40 of file bcm_rod_formatter.vhd.

Member Data Documentation

CLK in std_logic [Port] |

hola_CLK out std_logic [Port] |

hola_LDOWN in std_logic [Port] |

hola_LFF in std_logic [Port] |

hola_LRL in std_logic_vector ( 3 downto 0 ) [Port] |

hola_UCTRL out std_logic [Port] |

SLINK control word flag (UCTRL) !!! ACTIVE LOW !!!

Definition at line 80 of file bcm_rod_formatter.vhd.

hola_UD out std_logic_vector ( 31 downto 0 ) [Port] |

hola_UDW out std_logic_vector ( 1 downto 0 ) := " 00 " [Port] |

SLINK data width (UDW) "00"=32-bit, "01"=16-bit, "10"=8-bit, "11"=reserved.

Definition at line 82 of file bcm_rod_formatter.vhd.

hola_URESET out std_logic [Port] |

hola_UTEST out std_logic [Port] |

hola_UWEN out std_logic [Port] |

ieee library [Library] |

INPUT_DATA_WIDTH positive := 32 [Generic] |

MAX_FRAGMENT_SIZE std_logic_vector ( 11 downto 0 ) := x " 17f " [Generic] |

rod_CTP_trigger_type in std_logic_vector ( 31 downto 0 ) := x " 00000011 " [Port] |

rod_data_available in std_logic := ' 0 ' [Port] |

rod_data_next out std_logic := ' 0 ' [Port] |

rod_data_vld in std_logic [Port] |

rod_detector_event_type in std_logic_vector ( 31 downto 0 ) := x " 000000dd " [Port] |

ROD_EMPTY std_logic_vector ( 31 downto 0 ) := x " 00000000 " [Generic] |

rod_format_version in std_logic_vector ( 31 downto 0 ) := x " 03010001 " [Port] |

rod_fragment_end in std_logic := ' 0 ' [Port] |

ROD_HEADER std_logic_vector ( 31 downto 0 ) := x " ee1234ee " [Generic] |

ROD_HEADER_WORDS std_logic_vector ( 31 downto 0 ) := x " 00000009 " [Generic] |

rod_input_data in std_logic_vector ( INPUT_DATA_WIDTH -1 downto 0 ) [Port] |

rod_run_number in std_logic_vector ( 31 downto 0 ) := x " 7fffffff " [Port] |

rod_source_ID in std_logic_vector ( 31 downto 0 ) := x " 00810000 " [Port] |

ROD_STATUS_BLOCK_AFTER_DATA std_logic_vector ( 31 downto 0 ) := x " 00000001 " [Generic] |

ROD_STATUS_BLOCK_BEFORE_DATA std_logic_vector ( 31 downto 0 ) := x " 00000000 " [Generic] |

ROD_STATUS_BLOCK_WORD1 std_logic_vector ( 31 downto 0 ) := x " 12345678 " [Generic] |

ROD_STATUS_BLOCK_WORD2 std_logic_vector ( 31 downto 0 ) := x " 87654321 " [Generic] |

ROD_STATUS_BLOCK_WORDS std_logic_vector ( 31 downto 0 ) := x " 00000002 " [Generic] |

SCLR in std_logic [Port] |

SLINK_BEGIN_OF_FRAGMENT std_logic_vector ( 31 downto 0 ) := x " b0f00000 " [Generic] |

SLINK_END_OF_FRAGMENT std_logic_vector ( 31 downto 0 ) := x " e0f00000 " [Generic] |

std_logic_1164 package [Package] |

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 28 of file bcm_rod_formatter.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file bcm_rod_formatter.vhd.

The documentation for this class was generated from the following file: