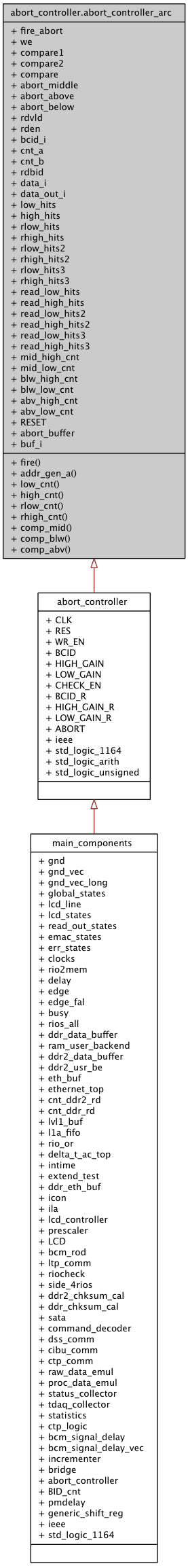

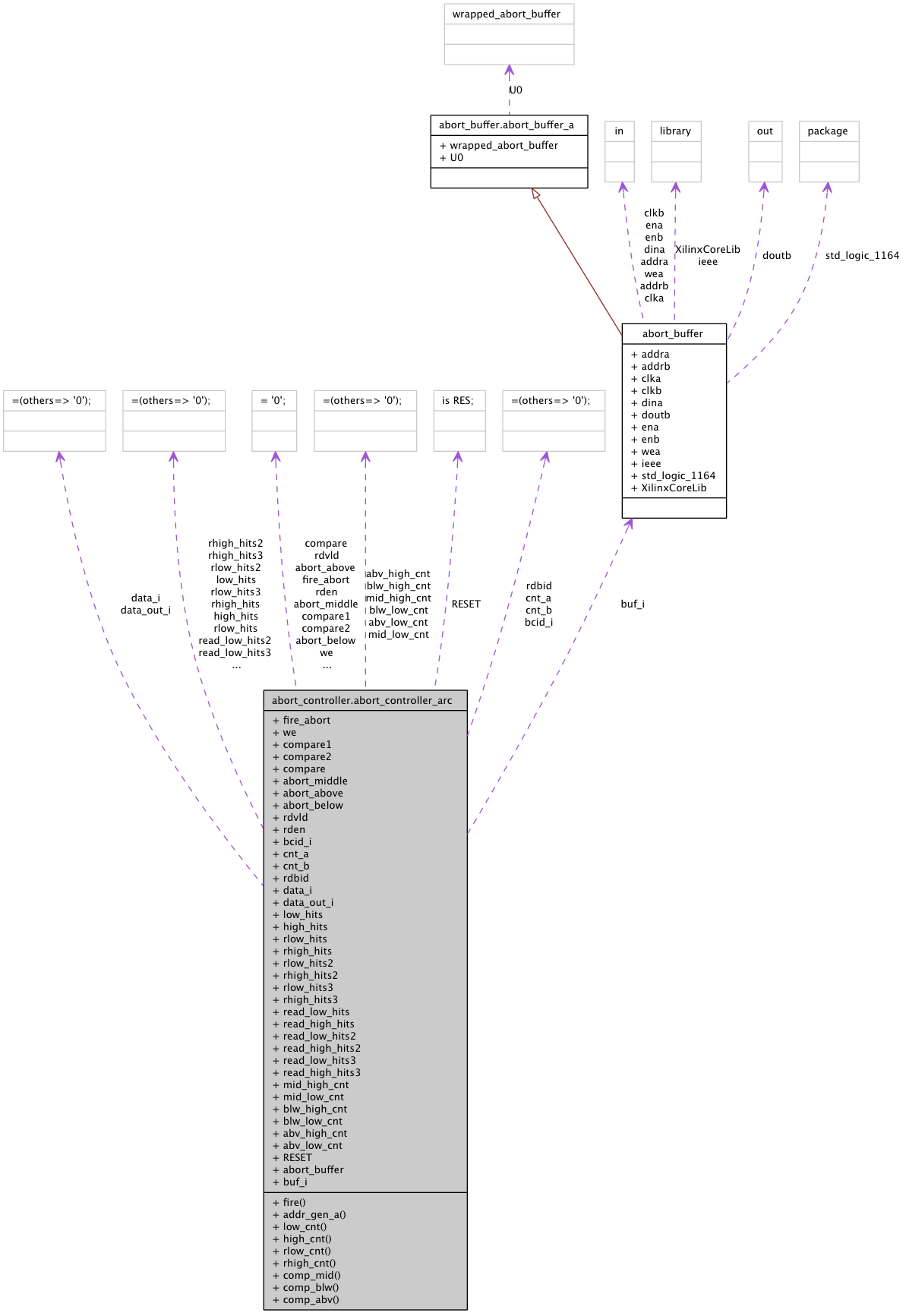

abort_controller.abort_controller_arc Architecture Reference

Beam abort logic. More...

Processes | |

| fire | ( CLK , RES ) |

| purpose: immediate abort | |

| addr_gen_a | ( CLK ) |

| addressing of write half with bcid | |

| low_cnt | ( CLK , RESET ) |

| count low gain hits | |

| high_cnt | ( CLK , RESET ) |

| count high gain hits | |

| rlow_cnt | ( CLK , RESET ) |

| count remote low gain hits | |

| rhigh_cnt | ( CLK , RESET ) |

| count remote high gain hits | |

| comp_mid | ( CLK , RESET ) |

| compare middle | |

| comp_blw | ( CLK , RESET ) |

| compare below | |

| comp_abv | ( CLK , RESET ) |

| compare above | |

Components | |

| abort_buffer | <Entity abort_buffer> |

| buffer to store results | |

Signals | |

| fire_abort | std_logic := ' 0 ' |

| we | std_logic := ' 0 ' |

| compare1 | std_logic := ' 0 ' |

| compare2 | std_logic := ' 0 ' |

| compare | std_logic := ' 0 ' |

| abort_middle | std_logic := ' 0 ' |

| abort_above | std_logic := ' 0 ' |

| abort_below | std_logic := ' 0 ' |

| rdvld | std_logic := ' 0 ' |

| rden | std_logic := ' 0 ' |

| bcid_i | std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| cnt_a | std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| cnt_b | std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| rdbid | std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| data_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| data_out_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| low_hits | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| high_hits | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| rlow_hits | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| rhigh_hits | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| rlow_hits2 | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| rhigh_hits2 | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| rlow_hits3 | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| rhigh_hits3 | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| read_low_hits | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| read_high_hits | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| read_low_hits2 | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| read_high_hits2 | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| read_low_hits3 | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| read_high_hits3 | std_logic_vector ( 2 downto 0 ) := ( others = > ' 0 ' ) |

| mid_high_cnt | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| mid_low_cnt | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| blw_high_cnt | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| blw_low_cnt | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| abv_high_cnt | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| abv_low_cnt | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

Component Instantiations | |

| buf_i | abort_buffer <Entity abort_buffer> |

| Circular Buffer, DP-RAM as a BRAM Core. | |

Aliases | |

| RESET | RES |

Detailed Description

Beam abort logic.Beam abort logic controller

Definition at line 53 of file abort_controller.vhd.

Member Function Documentation

| addr_gen_a | ( CLK ) |

addressing of write half with bcid

Definition at line 155 of file abort_controller.vhd.

00155 addr_gen_a : process(CLK) 00156 begin 00157 if CLK'event and CLK = '1' then 00158 if RES = '1' then 00159 cnt_a <= (others => '0'); 00160 data_i <= (others => '0'); 00161 bcid_i <= (others => '0'); 00162 else 00163 if WR_EN = '1' then 00164 bcid_i <= BCID; 00165 cnt_a <= bcid_i; 00166 data_i <= high_hits & low_hits; 00167 end if; 00168 end if; 00169 end if; 00170 end process addr_gen_a;

| comp_abv | ( CLK , | |

| RESET ) |

compare above

Definition at line 288 of file abort_controller.vhd.

00288 comp_abv : process (CLK, RESET) 00289 begin -- process comp_abv 00290 if RESET = '1' then -- asynchronous reset (active high) 00291 abort_above <= '0'; 00292 elsif CLK'event and CLK = '1' then -- rising clock edge 00293 if compare = '1' then 00294 abv_high_cnt <= conv_std_logic_vector(conv_integer(rhigh_hits3) + conv_integer(read_high_hits3), 5); 00295 abv_low_cnt <= conv_std_logic_vector(conv_integer(rlow_hits3) + conv_integer(read_low_hits3), 5); 00296 else 00297 abv_high_cnt <= (others => '0'); 00298 abv_low_cnt <= (others => '0'); 00299 end if; 00300 if abv_low_cnt >= 3 and abv_high_cnt >= 4 then 00301 abort_above <= '1'; 00302 else 00303 abort_above <= '0'; 00304 end if; 00305 end if; 00306 end process comp_abv;

| comp_blw | ( CLK , | |

| RESET ) |

compare below

Definition at line 267 of file abort_controller.vhd.

00267 comp_blw : process (CLK, RESET) 00268 begin -- process comp_blw 00269 if RESET = '1' then -- asynchronous reset (active high) 00270 abort_below <= '0'; 00271 elsif CLK'event and CLK = '1' then -- rising clock edge 00272 if compare2 = '1' then 00273 blw_high_cnt <= conv_std_logic_vector(conv_integer(rhigh_hits2) + conv_integer(read_high_hits2), 5); 00274 blw_low_cnt <= conv_std_logic_vector(conv_integer(rlow_hits2) + conv_integer(read_low_hits2), 5); 00275 else 00276 blw_high_cnt <= (others => '0'); 00277 blw_low_cnt <= (others => '0'); 00278 end if; 00279 if blw_low_cnt >= 3 and blw_high_cnt >= 4 then 00280 abort_below <= '1'; 00281 else 00282 abort_below <= '0'; 00283 end if; 00284 end if; 00285 end process comp_blw;

| comp_mid | ( CLK , | |

| RESET ) |

compare middle

Definition at line 243 of file abort_controller.vhd.

00243 comp_mid : process (CLK, RESET) 00244 begin -- process comp_mid 00245 if RESET = '1' then -- asynchronous reset (active high) 00246 abort_middle <= '0'; 00247 mid_high_cnt <= (others => '0'); 00248 mid_low_cnt <= (others => '0'); 00249 elsif CLK'event and CLK = '1' then -- rising clock edge 00250 abort_middle <= '0'; 00251 if compare1 = '1' then 00252 mid_high_cnt <= conv_std_logic_vector(conv_integer(rhigh_hits) + conv_integer(read_high_hits), 5); 00253 mid_low_cnt <= conv_std_logic_vector(conv_integer(rlow_hits) + conv_integer(read_low_hits), 5); 00254 else 00255 mid_high_cnt <= (others => '0'); 00256 mid_low_cnt <= (others => '0'); 00257 end if; 00258 if mid_low_cnt >= 3 and mid_high_cnt >= 4 then 00259 abort_middle <= '1'; 00260 else 00261 abort_middle <= '0'; 00262 end if; 00263 end if; 00264 end process comp_mid;

| fire | ( CLK , | |

| RES ) |

purpose: immediate abort

Definition at line 113 of file abort_controller.vhd.

00113 fire : process (CLK, RES) 00114 variable lowcnt : std_logic_vector(2 downto 0) := "000"; 00115 begin -- process fire 00116 if RES = '1' then -- asynchronous reset (active high) 00117 fire_abort <= '0'; 00118 lowcnt := "000"; 00119 elsif CLK'event and CLK = '1' then -- rising clock edge 00120 fire_abort <= '0'; 00121 lowcnt := "000"; 00122 if (HIGH_GAIN(0) and HIGH_GAIN(1) and HIGH_GAIN(2) and HIGH_GAIN(3)) = '1' then 00123 lowcnt := conv_std_logic_vector(conv_integer(LOW_GAIN(0)) + conv_integer(LOW_GAIN(1)) + conv_integer(LOW_GAIN(2)) + conv_integer(LOW_GAIN(3)), 3); 00124 if lowcnt >= 3 then 00125 fire_abort <= '1'; 00126 else 00127 lowcnt := "000"; 00128 fire_abort <= '0'; 00129 end if; 00130 else 00131 lowcnt := "000"; 00132 fire_abort <= '0'; 00133 end if; 00134 end if; 00135 end process fire;

| high_cnt | ( CLK , | |

| RESET ) |

count high gain hits

Definition at line 185 of file abort_controller.vhd.

00185 high_cnt : process (CLK, RESET) 00186 begin -- process high_cnt 00187 if RESET = '1' then -- asynchronous reset (active high) 00188 high_hits <= "000"; 00189 elsif CLK'event and CLK = '1' then -- rising clock edge 00190 if WR_EN = '1' then 00191 high_hits <= conv_std_logic_vector(conv_integer(HIGH_GAIN(0)) + conv_integer(HIGH_GAIN(1)) + conv_integer(HIGH_GAIN(2)) + conv_integer(HIGH_GAIN(3)), 3); 00192 end if; 00193 end if; 00194 end process high_cnt;

| low_cnt | ( CLK , | |

| RESET ) |

count low gain hits

Definition at line 173 of file abort_controller.vhd.

00173 low_cnt : process (CLK, RESET) 00174 begin -- process low_cnt 00175 if RESET = '1' then -- asynchronous reset (active high) 00176 low_hits <= "000"; 00177 elsif CLK'event and CLK = '1' then -- rising clock edge 00178 if WR_EN = '1' then 00179 low_hits <= conv_std_logic_vector(conv_integer(LOW_GAIN(0)) + conv_integer(LOW_GAIN(1)) + conv_integer(LOW_GAIN(2)) + conv_integer(LOW_GAIN(3)), 3); 00180 end if; 00181 end if; 00182 end process low_cnt;

| rhigh_cnt | ( CLK , | |

| RESET ) |

count remote high gain hits

Definition at line 209 of file abort_controller.vhd.

00209 rhigh_cnt : process (CLK, RESET) 00210 begin -- process rhigh_cnt 00211 if RESET = '1' then -- asynchronous reset (active high) 00212 rhigh_hits <= (others => '0'); 00213 elsif CLK'event and CLK = '1' then -- rising clock edge 00214 if CHECK_EN = '1' then 00215 rhigh_hits <= conv_std_logic_vector(conv_integer(HIGH_GAIN_R(0)) + conv_integer(HIGH_GAIN_R(1)) + conv_integer(HIGH_GAIN_R(2)) + conv_integer(HIGH_GAIN_R(3)), 3); 00216 end if; 00217 end if; 00218 end process rhigh_cnt;

| rlow_cnt | ( CLK , | |

| RESET ) |

count remote low gain hits

Definition at line 197 of file abort_controller.vhd.

00197 rlow_cnt : process (CLK, RESET) 00198 begin -- process rlow_cnt 00199 if RESET = '1' then -- asynchronous reset (active high) 00200 rlow_hits <= (others => '0'); 00201 elsif CLK'event and CLK = '1' then -- rising clock edge 00202 if CHECK_EN = '1' then 00203 rlow_hits <= conv_std_logic_vector(conv_integer(LOW_GAIN_R(0)) + conv_integer(LOW_GAIN_R(1)) + conv_integer(LOW_GAIN_R(2)) + conv_integer(LOW_GAIN_R(3)), 3); 00204 end if; 00205 end if; 00206 end process rlow_cnt;

Member Data Documentation

abort_buffer [Component] |

buf_i abort_buffer [Component Instantiation] |

The documentation for this class was generated from the following file: