ipmac Package Reference

Header with IP & MAC addresses. More...

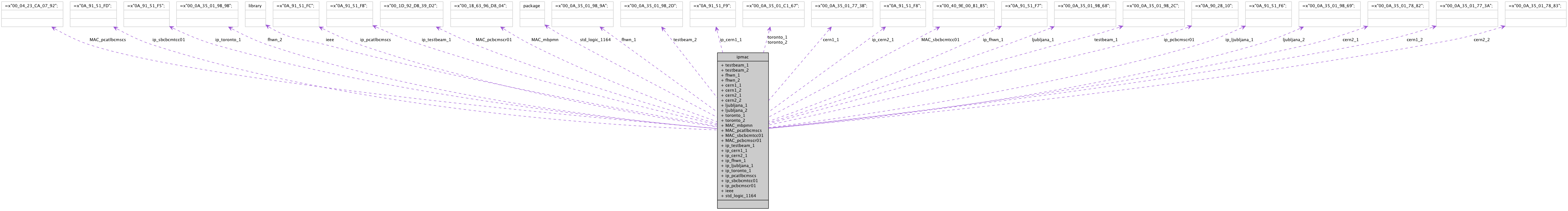

Collaboration diagram for ipmac:

Libraries | |

| ieee | |

| standard IEEE library | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

Constants | |

| testbeam_1 | std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_9B_2C " |

| FPGA MAC address top testbeam. | |

| testbeam_2 | std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_9B_2D " |

| FPGA MAC address bottom testbeam. | |

| fhwn_1 | std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_9B_9A " |

| FPGA MAC address top fhwn. | |

| fhwn_2 | std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_9B_9B " |

| FPGA MAC address bottom fhwn. | |

| cern1_1 | std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_77_3B " |

| FPGA MAC address top cern1. | |

| cern1_2 | std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_77_3A " |

| FPGA MAC address bottom cern1. | |

| cern2_1 | std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_78_82 " |

| FPGA MAC address top cern2. | |

| cern2_2 | std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_78_83 " |

| FPGA MAC address bottom cern2. | |

| ljubljana_1 | std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_9B_68 " |

| FPGA MAC address top ljubljana. | |

| ljubljana_2 | std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_9B_69 " |

| FPGA MAC address bottom ljubljana. | |

| toronto_1 | std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_C1_67 " |

| FPGA MAC address top toronto. | |

| toronto_2 | std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_C1_67 " |

| FPGA MAC address bottom toronto. | |

| MAC_mbpmn | std_logic_vector ( 47 downto 0 ) := x " 00_1B_63_96_D8_04 " |

| PC MAC address mbpmn. | |

| MAC_pcatlbcmscs | std_logic_vector ( 47 downto 0 ) := x " 00_04_23_CA_07_92 " |

| PC MAC address pcatlbcmscs. | |

| MAC_sbcbcmtcc01 | std_logic_vector ( 47 downto 0 ) := x " 00_40_9E_00_B1_B5 " |

| PC MAC address sbc-bcm-tcc-01. | |

| MAC_pcbcmscr01 | std_logic_vector ( 47 downto 0 ) := x " 00_1D_92_DB_39_D2 " |

| PC MAC address pc-bcm-scr-01. | |

| ip_testbeam_1 | std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_FB " |

| FPGA IP address testbeam. | |

| ip_cern1_1 | std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_F9 " |

| FPGA IP address cern1. | |

| ip_cern2_1 | std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_F8 " |

| FPGA IP address cern2. | |

| ip_fhwn_1 | std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_F7 " |

| FPGA IP address fhwn. | |

| ip_ljubljana_1 | std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_F6 " |

| FPGA IP address ljubljana. | |

| ip_toronto_1 | std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_F5 " |

| FPGA IP address toronto. | |

| ip_pcatlbcmscs | std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_FC " |

| PC IP address pcatlbcmscs. | |

| ip_sbcbcmtcc01 | std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_FD " |

| PC IP address sbc-bcm-tcc-01. | |

| ip_pcbcmscr01 | std_logic_vector ( 31 downto 0 ) := x " 0A_90_2B_10 " |

| PC MAC address pc-bcm-scr-01. | |

Detailed Description

Header with IP & MAC addresses.

Declaration of all IP & MAC addresses needed Hostnames & Addresses of FPGAs:

Board Host Name MAC Top MAC Bottom IP Top

Test-Beam FPGA-BCM-ROD-01 00_0A_35_01_9B_2C 00_0A_35_01_9B_2D 10.145.81.251

CERN 1 FPGA-BCM-ROD-02 00_0A_35_01_77_3B 00_0A_35_01_77_3A 10.145.81.249

CERN 2 FPGA-BCM-ROD-03 00_0A_35_01_78_82 00_0A_35_01_78_83 10.145.81.248

FHWN FPGA-BCM-ROD-04 00_0A_35_01_9B_9A 00_0A_35_01_9B_9B 10.145.81.247

Ljubljana FPGA-BCM-ROD-05 00_0A_35_01_9B_68 00_0A_35_01_9B_69 10.145.81.246

Toronto FPGA-BCM-ROD-05 00_0A_35_01_C1_67 00_0A_35_01_C1_68 10.145.81.245

Definition at line 47 of file ipmac.vhd.

Member Data Documentation

cern1_1 std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_77_3B " [Constant] |

cern1_2 std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_77_3A " [Constant] |

cern2_1 std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_78_82 " [Constant] |

cern2_2 std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_78_83 " [Constant] |

fhwn_1 std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_9B_9A " [Constant] |

fhwn_2 std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_9B_9B " [Constant] |

ip_cern1_1 std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_F9 " [Constant] |

ip_cern2_1 std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_F8 " [Constant] |

ip_fhwn_1 std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_F7 " [Constant] |

ip_ljubljana_1 std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_F6 " [Constant] |

ip_pcatlbcmscs std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_FC " [Constant] |

ip_pcbcmscr01 std_logic_vector ( 31 downto 0 ) := x " 0A_90_2B_10 " [Constant] |

ip_sbcbcmtcc01 std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_FD " [Constant] |

ip_testbeam_1 std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_FB " [Constant] |

ip_toronto_1 std_logic_vector ( 31 downto 0 ) := x " 0A_91_51_F5 " [Constant] |

ljubljana_1 std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_9B_68 " [Constant] |

ljubljana_2 std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_9B_69 " [Constant] |

MAC_mbpmn std_logic_vector ( 47 downto 0 ) := x " 00_1B_63_96_D8_04 " [Constant] |

MAC_pcatlbcmscs std_logic_vector ( 47 downto 0 ) := x " 00_04_23_CA_07_92 " [Constant] |

MAC_pcbcmscr01 std_logic_vector ( 47 downto 0 ) := x " 00_1D_92_DB_39_D2 " [Constant] |

MAC_sbcbcmtcc01 std_logic_vector ( 47 downto 0 ) := x " 00_40_9E_00_B1_B5 " [Constant] |

std_logic_1164 package [Package] |

testbeam_1 std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_9B_2C " [Constant] |

testbeam_2 std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_9B_2D " [Constant] |

toronto_1 std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_C1_67 " [Constant] |

toronto_2 std_logic_vector ( 47 downto 0 ) := x " 00_0A_35_01_C1_67 " [Constant] |

The documentation for this class was generated from the following file: